Scoprite con noi il codice di denominazione di RISC-V

L'architettura del set di istruzioni (ISA) RISC-V rappresenta un'opportunità straordinaria. La sua struttura consente agli sviluppatori di utilizzare processori di svariate dimensioni e con diverse prestazioni che offrono una compatibilità software mai sperimentata sinora. Il fattore chiave per sfruttare questa compatibilità è comprendere il codice di denominazione del core RISC-V.

A differenza della maggior parte delle architetture di processore, RISC-V è open-source, a disposizione degli sviluppatori senza bisogno di acquistare licenze o di pagare royalty. Inoltre, ISA è progettata per la flessibilità e consente agli sviluppatori di scegliere i blocchi di istruzioni che desiderano implementare e di omettere ciò di cui non hanno bisogno, persino di aggiungere istruzioni personalizzate se lo vogliono. Lo scopo è quello di stimolare lo sviluppo di più core di processori con dimensioni e attributi di prestazioni variabili che condividono una base comune.

Questa base comune offre un alto livello di compatibilità software tra i processori, a prescindere dal loro set di funzioni. Il codice per un processore RISC-V minimo che implementa solo il set di istruzioni intero, per esempio, girerà senza bisogno di modifiche su un processore più potente che è in grado di eseguire sia i numeri interi sia la virgola mobile. Il codice che utilizza le istruzioni a virgola mobile non potrà essere eseguito, naturalmente, su macchine a numeri interi ma non farà neppure andare in crash il processore. Le istruzioni non implementate genereranno semplicemente un'esecuzione di istruzioni non consentite, una trap.

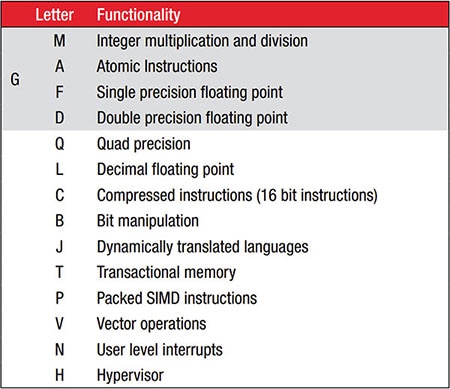

L'architettura ISA RISC-V raggiunge questa flessibilità eseguendo un partizionamento delle sue istruzioni in gruppi essenzialmente indipendenti con codici macchina non sovrapposti. Questi gruppi di istruzioni sono chiamati "estensioni standard" e ISA ha definito numerose di tali estensioni standard che forniscono la maggior parte della funzionalità di cui gli sviluppatori potrebbero avere bisogno. Ogni estensione standard è identificata da un codice alfabetico. L'estensione standard "M", per esempio, fornisce istruzioni per moltiplicare o dividere due numeri interi conservati nei registri. Analogamente, l'estensione standard "F" fornisce istruzioni per operazioni a virgola mobile a precisione singola.

Poiché gli sviluppatori di processori, quando implementano un core RISC-V, possono mettere insieme e abbinare variamente le estensioni standard, si potrebbe pensare che gli utilizzatori saranno costretti a leggere attentamente le schede delle specifiche e i manuali per stabilire che cosa il processore per cui intendono realizzare un progetto è in grado di fare realmente. Ma c'è una soluzione più semplice. RISC-V utilizza una convenzione per la numerazione che dichiara immediatamente agli utilizzatori le capacità del core.

La convenzione per la numerazione inizia dalle specifiche base. RISC-V ha definito quattro specifiche base:

- RV32I ha un set di istruzioni intero a 32 bit e offre 32 registri per uso generale;

- RV32E utilizza un set di istruzioni a 32-bit che ha come target applicazioni di tipo embedded con 16 registri;

- RV64I ha un set di istruzioni intero a 64 bit e 32 registri;

- RV128I ha un set di istruzioni intero a 128 bit e 32 registri.

Queste specifiche base definiscono un processore completamente funzionante, per quanto barebone. La maggior parte degli sviluppatori, tuttavia, sceglierà di aggiungere una o più estensioni del set di istruzioni standard al proprio progetto. Queste estensioni standard e le loro lettere identificative sono elencate nella Figura 1.

Figura 1: Le estensioni del set di istruzioni standard per i processori RISC-V utilizzano codici alfabetici per indicare la loro presenza in una convenzione per la numerazione dei core. (Immagine per gentile concessione di DigiKey)

Figura 1: Le estensioni del set di istruzioni standard per i processori RISC-V utilizzano codici alfabetici per indicare la loro presenza in una convenzione per la numerazione dei core. (Immagine per gentile concessione di DigiKey)

Una designazione completa del core di RISC-V è composta dalla specifica base a cui vengono aggiunte le lettere delle estensioni standard che implementa, nell'ordine elencato nella Figura 1. Un piccolo SoC che utilizza risorse minime, dunque, potrebbe essere denominato RV32EMAB. Ciò significa che il core implementa il set di istruzioni intero a 32 bit per i dispositivi embedded, ha 16 registri e gestisce la moltiplicazione e la divisione degli interi e le istruzioni atomiche. Non è capace di operazioni a virgola mobile ma supporta la manipolazione dei bit.

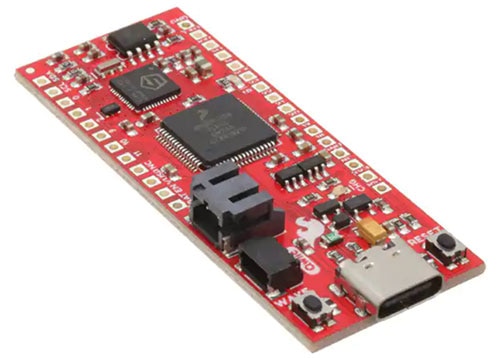

Perciò, quando un utilizzatore sceglie un chip RISC-V per il proprio progetto, deve solo controllare la designazione del core per capire quali sono le funzionalità che offre. Ad esempio, il processore della scheda di valutazione DEV-15799 FE310 Thing Plus RISC-V di SparkFun Electronics è tra i core RV32IMAC (Figura 2).

Figura 2: Il processore RISC-V della scheda DEV-15799 è denominato RV32IMAC, il che significa, tra le altre cose, che ha un set di istruzioni intero a 32 bit, 32 registri e che offre istruzioni atomiche. (Immagine per gentile concessione di SparkFun Electronics)

Figura 2: Il processore RISC-V della scheda DEV-15799 è denominato RV32IMAC, il che significa, tra le altre cose, che ha un set di istruzioni intero a 32 bit, 32 registri e che offre istruzioni atomiche. (Immagine per gentile concessione di SparkFun Electronics)

Ciò significa che dispone di un set di istruzioni intero a 32 bit, di 32 registri, che implementa operazioni di moltiplicazione e divisione degli interi, che offre istruzioni atomiche e supporta istruzioni compresse a 16 bit per ridurre al minimo lo spazio del codice. Qualsiasi codice sviluppato su questa scheda sarà in grado di girare su qualsiasi altro core RV32I con le estensioni standard per la moltiplicazione e l'accumulazione (MAC).

Un altro esempio è il modulo SoC Sipeed MAXIX-I RISC-V 114991684 di Seeed Technology, che descrive il suo core RISC-V come RV64IMAFDC. Ha un set di istruzioni a 64 bit con moltiplicazione e divisione degli interi, istruzioni atomiche, virgola mobile a singola e doppia precisione e istruzioni compresse. Il codice sviluppato per questo processore dovrebbe girare su qualsiasi processore RISC-V con le stesse designazioni del core, sebbene la mappatura della memoria delle periferiche e simili potrebbe necessitare di regolazione.

Conclusione

Avendo a disposizione il codice di designazione di RISC-V, gli utenti non dovrebbero avere difficoltà a iniziare le loro sperimentazioni con questa potente architettura. Abbinando i codici dei core, gli utenti possono avere la certezza che i loro sforzi di programmazione con un processore godranno di un'elevata portabilità verso altri processori RISC-V.

Per iniziare a sperimentare, vi consigliamo di dare un'occhiata a una fantastica risorsa, Guide to RISC-V, che ripercorre la configurazione iniziale e l'utilizzo di numerose e differenti schede di valutazione RISC-V.

Have questions or comments? Continue the conversation on TechForum, DigiKey's online community and technical resource.

Visit TechForum