Come l'estensione Atomic di RISC-V offre capacità superiori di manipolazione dei bit

L'architettura RISC-V si sta rapidamente diffondendo a macchia d'olio e per un buon motivo: la sua influenza nel settore sta aumentando.

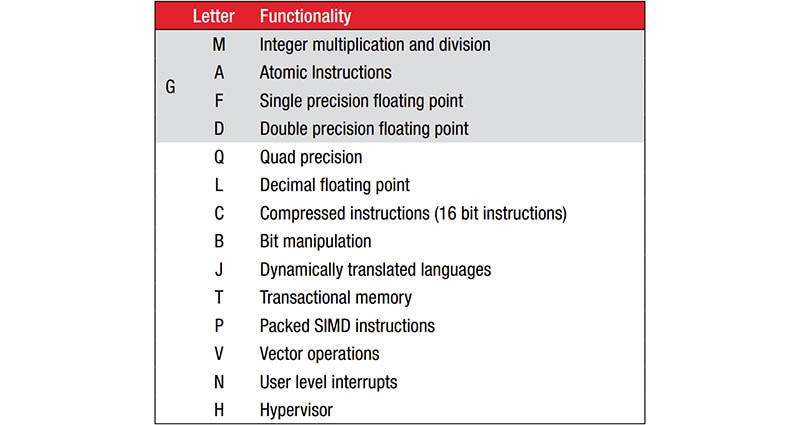

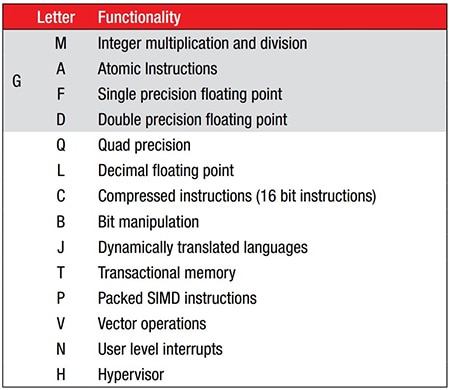

Oltre all'architettura core e alla sua architettura ISA (Instruction Set Architecture) realmente ridotta, è potenziata da una serie di estensioni standardizzate (Figura 1). Ad esempio, un core RISC-V a 32 bit (RV32) che supporta la virgola mobile a precisione singola e anche istruzioni compresse, secondo l'elenco di estensioni mostrato sarebbe designato RV32FC.

Figura 1: L'ISA di base del RISC-V è potenziata da una serie di estensioni di istruzioni standardizzate, indicate da una lettera come suffisso dopo il nome del core. (Immagine per gentile concessione di RISC-V.org)

Figura 1: L'ISA di base del RISC-V è potenziata da una serie di estensioni di istruzioni standardizzate, indicate da una lettera come suffisso dopo il nome del core. (Immagine per gentile concessione di RISC-V.org)

Per molte applicazioni di intelligenza artificiale (IA) e di apprendimento automatico (ML), così come per i sistemi embedded avanzati, le quattro estensioni più necessarie sono la moltiplicazione e la divisione degli interi (M), le istruzioni atomiche (A), la virgola mobile a precisione singola (F) e la virgola mobile a precisione doppia (D). Tuttavia, invece di designare un core come RV32MAFD, queste estensioni sono tutte raggruppate sotto il suffisso G, come in RV32G.

Per maggiori informazioni sulle varie estensioni e su RISC-V in generale, vedere l'e-book RISC-V di DigiKey nel sito EDU.

Per quanto mi riguarda, dato che la mia prima esperienza con i processori è stata con i sistemi embedded profondi, tendo a guardare attentamente il supporto di manipolazione dei bit di lettura-modifica-scrittura di un'architettura sulla memoria dati. Per queste applicazioni, è pratica diffusa impostare e cancellare bit per registri periferici e semafori. Senza istruzioni native di manipolazione dei bit, un core avrebbe bisogno di copiare il contenuto delle posizioni di memoria dati in un registro del core, impostare, cancellare o commutare i bit usando rispettivamente istruzioni OR, AND o XOR e poi memorizzare di nuovo il risultato nella posizione di memoria dati. Queste operazioni non solo richiedono più tempo, ma, per alcune applicazioni di controllo embedded, possono comportare anche un'esplosione del codice (code bloat) anche del 20%, come ho avuto modo di appurare di persona.

Per alcune applicazioni, il code bloat e la diminuzione delle prestazioni possono essere accettabili. Tuttavia, mentre queste tre istruzioni vengono elaborate, un interrupt può rimuovere bruscamente il controllo del programma dall'operazione oppure, ancora peggio, in un sistema multiprocessore un altro core potrebbe leggere da quella stessa posizione di memoria. Per disabilitare gli interrupt o bloccare la memoria per assicurarsi che questi eventi non corrompano la memoria dati sono richieste altre istruzioni, con conseguenti complicazioni che possono generare problemi di prestazioni.

Arm ha tentato di risolvere questi problemi implementando il bit banding, che funziona per le operazioni di bit semplici. A mio avviso, però, RISC-V ha implementato una soluzione più elegante e flessibile.

Perché l'estensione Atomic è così elegante

L'estensione RISC-V A (Atomic) supporta due operazioni: un'istruzione Load-Reserved/Store-Conditional, di cui non ci occuperemo qui, e un'istruzione binary/bitwise che fornisce una manipolazione semplice dei bit sulla memoria dati. Mentre l'estensione per la manipolazione dei bit di RISC-V B supporta una serie di istruzioni complesse di controllo dei bit, l'estensione Atomic non riguarda solo i sistemi multiprocessore. È utile anche nei sistemi embedded più piccoli, dove le esigenze di manipolazione dei bit sono più semplici. Un esempio di questo sistema è il modulo RISC-V dual-core a 64 bit 114991684 di Seeed Technology. Ha due core RV64GC che devono lavorare insieme e funzionare bene con la SRAM dati condivisa.

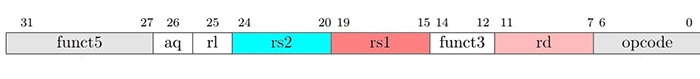

Il formato dell'operazione di memoria atomica (AMO) dell'estensione A di RISC-V è mostrato nella Figura 2.

Figura 2: Il formato di istruzioni RISC-V AMO supporta operazioni binarie atomiche sulla memoria dati con una sola istruzione. (Immagine per gentile concessione di RISC-V.org - migliorata da Bill Giovino)

Figura 2: Il formato di istruzioni RISC-V AMO supporta operazioni binarie atomiche sulla memoria dati con una sola istruzione. (Immagine per gentile concessione di RISC-V.org - migliorata da Bill Giovino)

AMO è una potente istruzione di lettura-modifica-scrittura che supporta varie operazioni binarie direttamente sulla memoria dati a cui si punta in rs1 con una sola istruzione. Facendo riferimento alla Figura 2, l'operazione carica il contenuto della posizione di indirizzo della memoria dati in rs1 e memorizza il valore nel registro rd. Esegue poi un'operazione binaria sul valore di rd con il valore in rs2 e rimemorizza il risultato in rd nella posizione dell'indirizzo dei dati di memoria in rs1.

Le operazioni bitwise supportate sono OR (bit set), AND (bit clear) e XOR (bit toggle). Questo permette la manipolazione atomica di uno o più bit direttamente sulla memoria dati. Inoltre impedisce conflitti di memoria quando i due core RV64GC usano contemporaneamente lo stesso indirizzo di memoria. Oltre a semplificare le operazioni di semaforo, è estremamente utile per piccole applicazioni embedded quando si configurano i registri periferici nella memoria.

Altre operazioni supportate dall'AMO di RISC-V sono massimo intero, minimo intero e swap. È supportato anche l'ADD binario che permette l'addizione binaria diretta, incluso l'incremento diretto di un contatore nella memoria dati.

Il core RV64 supporta operazioni sia a 32-bit che a 64-bit. Per la manipolazione di bit con RV64, è importante che operi solo su dati a 64 bit, poiché l'operazione effettuerà il sign-extend di dati a 32 bit posti in rd.

Conclusione

L'ISA RISC-V è il primo serio rivale dell'ISA Arm. Le sue estensioni ISA forniscono un metodo standardizzato per migliorare il core con istruzioni che possono migliorare le prestazioni di un'applicazione. Sono particolarmente entusiasta dell'estensione opzionale Atomic.

Oltre a essere utile e quasi necessaria per i sistemi multiprocessore, l'estensione Atomic è anche un modo efficiente di fornire il controllo della manipolazione dei bit direttamente sulla memoria dati. Offre un vantaggio significativo rispetto a molte architetture esistenti, riducendo la dimensione del codice e migliorando le prestazioni.

Have questions or comments? Continue the conversation on TechForum, DigiKey's online community and technical resource.

Visit TechForum