RISC-V sposa l'intelligenza artificiale e l'apprendimento automatico grazie a una scheda di sviluppo dual core a 64 bit per la visione e l'udito artificiali

RISC-V è l'ultima arrivata nell'ondata di rinnovato interesse per i core a 32 bit. Ma questa volta si tratta di un ambiente di sviluppo diverso. Le recenti innovazioni e la competizione intorno ai core si sono focalizzate sul mercato consolidato dei microcontroller per uso generale, con periferiche generiche adatte a robuste applicazioni automotive. Tuttavia, l'attuale panorama embedded ruota intorno agli endpoint dell'Internet delle cose (IoT) ed è orientato verso i sofisticati sistemi industriali di edge computing. Invece di timer e interfacce seriali generiche, gli ultimi microcontroller RISC-V supportano anche periferiche sofisticate, comprese le capacità dei motori inferenziali per l'intelligenza artificiale (IA) e l'apprendimento automatico (ML).

RISC-V offre, tuttavia, ulteriori vantaggi che trascendono le evoluzioni del mercato e le richieste di natura tecnica. Prima di approfondire l'argomento, diamo un'occhiata al punto da dove siamo partiti.

Una breve incursione nella storia delle innovazioni dei microcontroller

Ogni pochi anni, il mercato dei microcontroller embedded vive una rivoluzione, che non rispetta tempi precisi e che non risponde solo a esigenze di maggiori prestazioni e funzionalità ma anche a fattori commerciali. A partire dal venerando 8051, il mercato degli 8 bit ha dominato i sistemi embedded quasi in ogni settore, incluso quello automotive, dei giochi e delle apparecchiature elettroniche; ad oggi, il microcontroller a 8 bit a bassissima potenza è presente ovunque e persino l'8051 continua a far registrare numeri notevoli, come vedremo più avanti.

Il microcontroller a 16 bit ha rappresentato a lungo il punto di incontro tra bassa potenza e prestazioni e ad oggi rimane un mercato sottovalutato da molti fornitori che non rientrano tra i protagonisti del settore. E poi sono venuti i processori a 32 bit, che si sono affermati al di fuori del settore dei personal computer grazie a una serie di architetture proprietarie nel corso delle guerre dei core degli anni 90 del Novecento e dei primi anni del 2000.

L'avvento di Arm ha messo fine alle guerre tra i core a 32 bit. Vista l'ampia offerta di fornitori, tutti più o meno riuniti sotto un'unica architettura, a vincere sono stati i clienti, che hanno avuto la possibilità di cambiarli senza doversi impegnare troppo a trasferire il proprio codice, un indubbio vantaggio rispetto alle architetture proprietarie.

RISC-V riduce veramente il set di istruzioni

Per molto tempo, la quota di mercato di RISC-V non è stata particolarmente brillante, soprattutto perché il mercato non sentiva alcuna esigenza di una nuova architettura del set di istruzioni (ISA) a 32 bit. Tuttavia, qualsiasi ingegnere che analizzasse l'architettura del core del RISC-V non poteva che rimanerne immediatamente colpito.

Storicamente RISC ha avuto il significato di Reduced Instruction Set Core/Computer (core/computer con set ridotto di istruzioni), che equivale a dire che ha solo le istruzioni minime necessarie per eseguire operazioni utili. A partire dagli albori, molte delle architetture che ora ricadono sotto RISC si sono allontanate da quella definizione ed hanno così tante istruzioni complesse da aver portato gli ingegneri a considerare l'etichetta con un certo cinismo. Ma l'ISA RISC-V è talmente fedele alla sua definizione che ci pare quasi di sentire nella nostra testa la voce di James Earl Jones che recita: "Impressionante. Molto impressionante".

RISC-V versione base a 32 bit ha 32 registri da 32 bit, da x0 a x31, di cui 31 per uso generale, mentre il registro x0 è cablato allo zero. Scavando più a fondo nel set di istruzioni di RISC-V, potrete apprezzare la saggezza di x0 = 0 e perché x0 sia un operando necessario per molte istruzioni che riescono a mantenere tale il set ridotto di istruzioni. Ma di ciò parleremo un'altra volta.

Il settore dei semiconduttori è globale e ha molte sane interdipendenze; tuttavia, i fornitori di semiconduttori, per ragioni che sono al tempo stesso ovvie e più sottili, desiderano mantenere un maggior controllo sui propri prodotti, compresa una più attenta valutazione dei costosi accordi di licenza e delle fonti di proprietà intellettuale che vengono vendute e rivendute. Alla luce di ciò, RISC-V è l'architettura giusta al momento giusto, grazie alla sua natura di ISA personalizzabile, open-source e non soggetta a royalty. È talmente vero che DigiKey sta dando molto risalto a RISC-V sul proprio sito EDU con un e-book su RISC-V — "Academic Components Reference Guide: RISC-V" — che presenta sia a sviluppatori agli esordi sia agli esperti gli strumenti di RSC-V e i kit di valutazione. Grazie a questi strumenti, gli sviluppatori che non hanno esperienze pregresse con questa architettura possono acquisire velocemente familiarità con il modello di programmazione RISC-V e ISA.

RISC-V: un core potente per l'intelligenza artificiale e l'apprendimento automatico

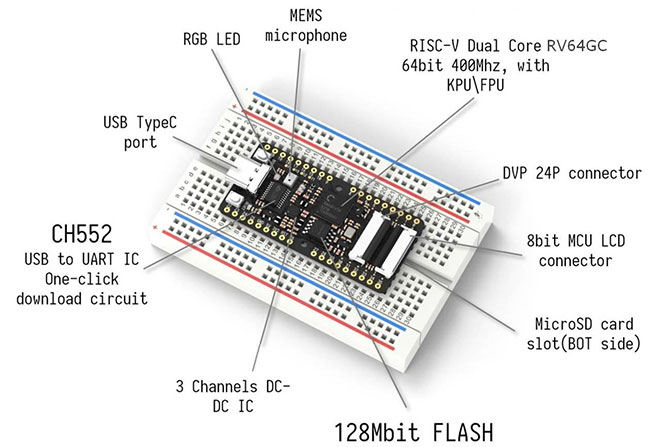

In genere una nuova ISA si presenta sul mercato con microcontroller per uso generale, dotati di una scheda di valutazione con tanti graziosi LED che lampeggiano; ma RISC-V punta direttamente all'IA e al ML. Seeed Technology, ad esempio, per rendere possibile l'apprendimento automatico, si affida alla scheda di sviluppo Seed 110991190 Sipeed Maix-BiT basata su RISC-V RV64I, un'ISA con indirizzo e dati da 64 bit con registri core da x0 a x31 da 64 bit (Figura 1).

Figura 1: La scheda di sviluppo Sipeed Maix-BiT di Seeed Technology si basa su un RISC-V RV64GC dual core e si rivolge ad applicazioni per la visione artificiale e l'apprendimento automatico. (Immagine per gentile concessione di Seeed Technology)

Figura 1: La scheda di sviluppo Sipeed Maix-BiT di Seeed Technology si basa su un RISC-V RV64GC dual core e si rivolge ad applicazioni per la visione artificiale e l'apprendimento automatico. (Immagine per gentile concessione di Seeed Technology)

Come afferma anche l'e-book su RISC-V di DigiKey a partire da pagina 5, le dimensioni ridotte di questa piccola scheda e le sue alte prestazioni la rendono adatta alle applicazioni IoT per l'elaborazione edge.

Il processore core per la scheda Sipeed Maix-BiT è un System-on-Chip (SoC) dual core RV64GC con microcontroller, in cui il suffisso G specifica che supporta estensioni per uso generale di moltiplicatori e divisori hardware, istruzioni atomiche per leggere, modificare e scrivere sulla memoria e per la virgola mobile a precisone singola e doppia. Il suffisso C indica che il microcontroller supporta istruzioni a 16 bit compresse, utili per scrivere codice compatto. Il microcontroller può accedere a 6 mebibyte (MiB) di SRAM su chip per uso generale oltre a 128°megabit (Mbit) di memoria flash per programmi esterni. Si tratta di una potenza di calcolo impressionante per un'ISA relativamente nuova e di una memoria sufficiente per applicazioni complesse di edge computing.

Ciò che rende veramente straordinario il microcontroller dual core RV64GC è un processore a rete neurale IA su chip per uso generale progettato per rilevare facce e oggetti in tempo reale. Il processore IA ha 2 MiB di SRAM dedicata per l'esecuzione di operazioni di IA, che rappresenta un'impressionante quantità di potenza di calcolo accessibile a chiunque possegga abilità medie di programmazione.

La scheda Sipeed Maix-BiT include uno slot per schede micro SD per l'espansione della memoria flash. Un microfono MEMS (sistema microelettromeccanico) su scheda può essere usato insieme con l'unità IA per applicazioni di udito artificiale, compresi sistemi complessi di riconoscimento della voce e del rumore. Il kit comprende anche una videocamera esterna che si collega a un connettore per la porta video digitale (DVP) nella parte inferiore della scheda venendo in aiuto alle applicazioni complesse di visione artificiale, un vantaggio nei sistemi di elaborazione edge per l'IoT.

La scheda è anche dotata di un'interfaccia USB per la programmazione e il debugging, che si interfaccia con RV64GC dual core tramite un chip USB-UART. È presente anche un connettore aggiuntivo per il display LCD esterno incluso, che rende possibile una retroazione visiva durante lo sviluppo di programmi e può anche essere usato nell'applicazione per la retroazione dell'utente.

Conclusione

È passata molta acqua sotto i ponti dai giorni del microcontroller a 8 bit. L'architettura ISA RISC-V saprà guadagnarsi il proprio posto accanto ad Arm in un mercato sanamente competitivo? Con tutto l'interesse suscitato da RISC-V e dalle schede avanzate di sviluppo come quella di cui abbiamo parlato, sembra certo che questa architettura abbia l'impeto che le consente di posizionarsi sul mercato, ma la discussione è più complessa. Ora come ora, grazie a proposte come la 110991190 Sipeed Maix-BiT di Seeed, sembra che si faccia strada nelle applicazioni IoT e IA/ML dell'edge.

Dimenticavo. A testimonianza dell'ubiquità dei dispositivi a 8 bit, sia il CI dell'interfaccia LCD sia il CI USB-UART di CH552 sulla scheda di sviluppo sono microcontroller preprogrammati a 8 bit. E CH552 è in realtà un venerando 8051.

Have questions or comments? Continue the conversation on TechForum, DigiKey's online community and technical resource.

Visit TechForum