MCU per l'Internet delle cose: piccole dimensioni, grande impatto

Contributo di Electronic Products

2015-01-21

Gli MCU sono gli elementi chiave per qualsiasi dispositivo connesso e ci si aspetta che permettano l'implementazione di milioni di "nodi finali" per l'Internet delle cose (IoT). I nodi finali comprendono un'ampia gamma di elementi quali misuratori, sensori, display e preprocessori, nonché componenti per la fusione di dati che combinano più funzioni in un singolo dispositivo. Un requisito comune nei nodi finali IoT è l'esigenza di dimensioni compatte, dal momento che questi dispositivi sono generalmente vincolati ad un ingombro molto ridotto. Consideriamo, ad esempio, i dispositivi indossabili: le dimensioni compatte e il peso contenuto sono caratteristiche essenziali per il successo del prodotto presso i clienti finali.

Gli MCU in contenitori compatti costituiscono l'elemento perfetto per il controllo delle applicazioni per nodi finali IoT con vincoli di dimensioni. Molti MCU dispongono inoltre di funzioni aggiuntive che semplificano l'inserimento di un progetto molto potente in un fattore di forma con vincoli di pin. L'assegnazione flessibile dei pin, il funzionamento autonomo e l'interconnessione intelligente delle periferiche sono alcuni esempi di caratteristiche avanzate di cui dispongono gli MCU con basso numero di pin, in grado di potenziare ulteriormente la loro capacità di avere un grande impatto sulle applicazioni con vincoli di dimensioni.

Contenitori con basso numero di pin

I contenitori di piccole dimensioni sono un elemento fondamentale per l'inserimento degli MCU nello spazio su scheda limitato disponibile con la maggior parte degli endpoint dell'IoT. I dispositivi indossabili, in particolare, dispongono di uno spazio molto limitato, ma hanno comunque bisogno di una notevole potenza di elaborazione e di uno spazio di storage significativo per implementare le funzioni front-end richieste dai sensori, dagli aggregatori di rilevamento e dai controller. I contenitori CSP forniscono un ingombro ultracompatto senza richiedere particolari capacità produttive. La famiglia di MCU in contenitore CSP a 20 pin Kinetis KL03 di Freescale, ad esempio, utilizza un formato CSP a 20 pin di 1,6 x 2,0 mm. Come illustrato nella Figura 1, il dispositivo a 20 pin ha 20 bump di saldatura a passo piccolo per poter occupare uno spazio su scheda minimo.

Le dimensioni compatte dei contenitori non implicano necessariamente una potenza di elaborazione limitata. KL03 ha un potente processore ARM Cortex-M0 a 32 bit e 48 MHZ con 32 kB di memoria flash su chip e 2 kB di SRAM su chip. Le porte seriali multiple (LPUART, SPI, I²C) semplificano la connessione dell'MCU alle periferiche standard. Un ADC a 12 bit con un comparatore analogico e un riferimento di tensione interno supporta i comuni requisiti di rilevamento. Le operazioni di temporizzazione, molto comuni nelle applicazioni IoT, sono supportate mediante un timer a bassa potenza e un clock in tempo reale. Per semplificare le applicazioni di controllo meccanico è disponibile anche un timer a modulazione di larghezza di impulso (PWM). Tutta questa potenza in un formato CSP a 20 pin molto compatto è un esempio eccellente delle grandi capacità a disposizione dei progettisti.

Integrazione intelligente

I produttori di MCU non si limitano, tuttavia, a offrire CPU potenti in contenitori compatti. Un altro modo per offrire le stesse funzionalità occupando un piccolo spazio su scheda è l'aggiunta dell'integrazione intelligente, ovvero di hardware specializzato in grado di ridurre al minimo il numero di dispositivi di supporto esterni. Ad esempio, quante volte vi è capitato di aver bisogno di pochi semplici componenti aggiuntivi per combinare funzioni esterne in modo tale che possano entrare in un dispositivo dalla piedinatura limitata? Vi è capitato di doverlo fare anche per accelerare l'elaborazione dei segnali di ingresso quando gli anelli di rilevamento bit gestiti dalla CPU erano troppo lenti o consumavano troppo prezioso tempo della CPU? I produttori di MCU stanno iniziando a rispondere a queste esigenze di maggiore integrazione logica con l'aggiunta della logica utente su chip.

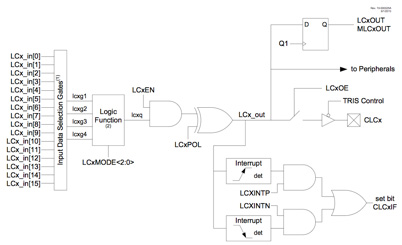

Un esempio di questo tipo di integrazione intelligente è l'MCU PIC16(L)F1503 di Microchip. Questo dispositivo include una piccola quantità di logica configurabile, mediante quelle che vengono chiamate celle logiche configurabili (o CLC). Queste celle logiche possono essere utilizzate per creare semplici funzioni logiche dai segnali interni e dagli ingressi del dispositivo. Le uscite CLC sono disponibili per l'uso in corrispondenza delle uscite del dispositivo oppure con periferiche interne. Nella Figura 2 è illustrato un diagramma di una CLC.

È possibile selezionare fino a 16 ingressi, quindi è disponibile una funzione logica per creare quattro uscite generate. Ciascuna uscita può essere abilitata singolarmente; è inoltre possibile selezionarne la polarità, rilevarne i limiti o registrarla, in base all'utilizzo che viene fatto dell'uscita. Le otto possibili funzioni logiche comprendono una selezione di AND-OR, OR-XOR, chiusure e registri, ovvero tutte le funzioni comuni necessarie su un dispositivo con piedinatura limitata. Ad esempio, è possibile integrare nell'MCU alcuni semplici gate sulla scheda oppure è possibile creare alcune semplici funzioni per eliminare i cicli della CPU normalmente utilizzati per combinare o condizionare gli ingressi del dispositivo.

Tenere presente che le periferiche possono ora essere combinate utilizzando l'hardware, invece di tecniche di "bit banging" e di polling ad uso intensivo della CPU. Questo rende le periferiche semplici molto più intelligenti e in grado di operare in modo indipendente dalla supervisione della CPU. Ora è possibile combinare agevolmente un ADC, un timer e un controller di interrupt in un sottosistema di rilevamento completo, con l'intervento della CPU necessario solo quando richiesto dal sottosistema, ad esempio quando si verifica una condizione di timeout o di superamento dei limiti.

Per una panoramica dell'impegno di Microchip nel campo della logica configurabile, vedere il Modulo didattico per l'uso dei prodotti dedicato alla "Cella logica configurabile".

Allocazione efficiente dei pin

Uno dei principali problemi dell'utilizzo di un MCU dal numero di pin contenuto è la difficoltà di associare la funzione corretta ad un pin di I/O. In molti MCU uno stesso pin di uscita viene condiviso da più periferiche ed è possibile che le periferiche che si desidera utilizzare abbiano assegnazioni I/O in conflitto tra loro. Ciò può rendere difficile ottenere tutte le funzionalità desiderate nel contenitore più compatto. Può essere necessario ricorrere ad un contenitore di dimensioni maggiori per poter disporre della combinazione di risorse desiderata. L'assegnazione I/O può avere un impatto anche sul layout della scheda e sull'instradamento dei segnali. Nel caso in cui i pin non abbiano una disposizione comoda, è possibile che si finisca per utilizzare uno spazio su scheda o un numero di strati di segnale maggiori di quanto non sia ideale.

Per risolvere queste limitazioni, alcuni produttori di MCU stanno iniziando ad aumentare la flessibilità dell'assegnazione dei pin. NXP, ad esempio, ha aggiunto una matrice di pin di I/O che può essere utilizzata per "sostituire" le posizioni dei pin per un'ampia gamma di segnali di periferiche su chip. Così come è disponibile nella famiglia LPC82x di NXP (Figura 3), la matrice di switch di I/O offre una capacità di sostituzione su 29 pin di I/O. I segnali GPIO, i timer, le periferiche seriali e persino gli ingressi analogici possono essere arbitrariamente commutati sul pin desiderato del dispositivo.

La matrice di switch fornisce connettività completa da qualunque dei 29 pin di I/O a qualunque delle periferiche interne. Vi sono solo alcune eccezioni: ad esempio, i pin JTAG sono sempre assegnati da PIO_0 a PIO_4 quando il componente è in modalità di scansione limite (boundary scan) e PIO_4 viene utilizzato per la riattivazione dallo spegnimento profondo; queste eccezioni sono comprensibili, dal momento che le funzioni associate dipendono così tanto dal dispositivo. La matrice di switch è talmente flessibile che è persino possibile assegnare più ingressi periferica allo stesso pin del dispositivo per ridurre ulteriormente il numero di pin. L'inclusione di una matrice di switch sull'MCU LPC82x migliora drasticamente la capacità di ottenere il segnale giusto sul pin giusto, permettendo di utilizzare il contenitore più piccolo possibile e di occupare il minimo spazio su scheda per la specifica applicazione.

NXP offre inoltre ai progettisti un Modulo didattico di "Introduzione alla matrice di switch I/O", disponibile sul sito Web DigiKey.

Funzionamento delle periferiche autonome

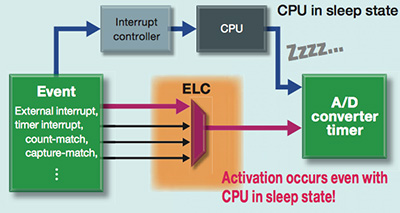

L'uso efficiente dei pin dell'MCU può essere supportato anche dalle funzionalità hardware dell'MCU che collegano i pin di ingresso e le periferiche interne. Ciò permette la creazione di periferiche autonome con uso efficiente dei pin tali da richiedere un intervento della CPU minimo se non nullo. Consideriamo ora la famiglia di MCU RL78/G13 di Renesas (ed esempio, R5F1007DANA#U0), che dispone di un controller ELC (Event Link Controller) che seleziona vari eventi (come interrupt di ingresso esterni, interrupt interni, interrupt del timer o risultati di confronto corrispondenze) e li connette tramite hardware all'ingresso periferica desiderato. Come illustrato nella Figura 4, utilizza un interrupt esterno per attivare la conversione da analogico a digitale. Questo risultato può essere ottenuto senza coinvolgere la CPU, addirittura con la CPU in modalità di sospensione a basso consumo. Ciò permette un uso efficiente delle risorse I/O, mantenendo al contempo al minimo la dissipazione di potenza, altro requisito chiave per la maggior parte delle applicazioni IoT.

Riepilogo

I contenitori a basso numero di pin sono ideali per molte applicazioni IoT ed è possibile utilizzare questi contenitori compatti senza dover rinunciare alla potenza di elaborazione. La mappatura efficiente dei pin tramite una matrice di switch I/O, un controller ELC o celle logiche configurabili (CLC) può migliorare l'efficienza dei pin per far sì che venga utilizzato il minimo spazio su scheda possibile nelle applicazioni IoT con maggiori vincoli di dimensioni.

Per ulteriori informazioni sui componenti discussi in questo articolo, utilizzare i collegamenti forniti per l'accesso alle pagine di prodotto sul sito DigiKey.

Esonero della responsabilità: le opinioni, le convinzioni e i punti di vista espressi dai vari autori e/o dai partecipanti al forum su questo sito Web non riflettono necessariamente le opinioni, le convinzioni e i punti di vista di DigiKey o le sue politiche.