Come implementare l'Edge IA su FPGA con strumenti familiari

Contributo di Editori nordamericani di DigiKey

2026-02-17

L'Edge IA, ovvero l'intelligenza artificiale ai margini della rete, raramente significa solo inferenza. Le implementazioni nel mondo reale tipicamente comprendono input/output (I/O) ad alta velocità, condizionamento del segnale e anelli di controllo in tempo reale, tutti eseguiti simultaneamente. Questi carichi di lavoro multifunzione richiedono una stretta coordinazione e livelli di determinismo che i progettisti trovano difficili da soddisfare utilizzando l'hardware IA tradizionale.

Due fattori aggravano il problema. In primo luogo, i modelli IA evolvono a un ritmo incalzante, spingendo i progettisti ad adottare piattaforme che supportino rapidi aggiornamenti degli algoritmi. Allo stesso tempo, molti sistemi edge rimangono sul campo per un decennio o anche più, rendendo difficile garantire l'adattabilità a lungo termine. In secondo luogo, il percorso dal modello addestrato al sistema implementato rimane frammentato. I data scientist lavorano in PyTorch e TensorFlow, mentre i team embedded utilizzano toolchain completamente differenti, creando attriti durante i trasferimenti che rallentano i tempi di produzione.

Per affrontare queste sfide sono necessarie piattaforme che combinino l'elaborazione IA ad alto throughput con comportamento deterministico, I/O flessibile e adattabilità a lungo termine, il tutto entro gli inviluppi di potenza limitati tipici delle implementazioni edge.

Questo articolo evidenzia le applicazioni e i requisiti associati che spingono i progettisti a esplorare nuove architetture di intelligenza artificiale. Il documento presenta quindi i dispositivi gate array programmabili sul campo (FPGA) abilitati per l'Edge IA e gli strumenti software di Altera e mostra come possono essere utilizzati per soddisfare le esigenze di queste applicazioni in un'ampia gamma di prestazioni e punti di potenza.

L'evoluzione dell'Edge IA richiede innovazione architetturale

I sistemi edge impiegano sempre più spesso tecniche di IA diversificate, il classico apprendimento automatico (ML) per il rilevamento delle anomalie, le reti neurali convoluzionali (CNN) per la percezione e i trasformatori per i modelli linguistici di grandi dimensioni (LLM). Questi algoritmi ad alta intensità di calcolo spesso coesistono con funzioni non-IA impegnative, come l'elaborazione dei segnali, la connettività di rete e il controllo in tempo reale.

I sistemi autonomi ne sono un esempio lampante. Spesso hanno bisogno di acquisire dati da sensori in molteplici modalità (es. video, audio, radar, LiDAR e retroazione di movimento/posizione), preelaborare questi flussi ad alto throughput, analizzare i risultati con una IA sofisticata e quindi gestire anelli di controllo di alta precisione, il tutto con un determinismo affidabile.

Molti esempi simili si trovano nelle applicazioni di automazione industriale, imaging medicale, difesa e telecomunicazioni. Un tema comune è che i carichi di lavoro convergenti sono difficili da gestire con le architetture tradizionali.

Gli FPGA sono particolarmente adatti all'Edge IA

Al contrario, questi requisiti si adattano bene alle capacità degli FPGA. In sostanza, gli FPGA forniscono una logica configurabile che esegue le operazioni realmente in parallelo, con un comportamento di temporizzazione integrato al momento della progettazione anziché fluttuare durante l'esecuzione. Questa architettura consente il determinismo a bassa latenza, fondamentale per l'Edge IA. La logica flessibile sfrutta anche l'I/O potente: gli FPGA offrono generalmente una grande quantità di I/O ad alta velocità in grado di interfacciarsi con un'ampia gamma di sensori e attuatori, fornendo un accoppiamento stretto con l'elaborazione IA.

Gli FPGA contengono anche una memoria interna distribuita, che mantiene i dati vicini alla logica che li utilizza. In questo modo si riducono i colli di bottiglia che si verificano quando più fasi di elaborazione devono competere per l'accesso a un bus di memoria condiviso, un vincolo comune nelle architetture basate su processori.

Molti FPGA incorporano anche hardware specializzato nell'elaborazione dei segnali digitali (DSP). Questi circuiti rinforzati garantiscono prestazioni più elevate e una migliore efficienza energetica per i carichi di lavoro di elaborazione dei segnali rispetto al tessuto per uso generale. Alcuni FPGA integrano anche sistemi di processori cablati che possono eseguire stack di software standard, incluso Linux, consentendo lo sviluppo di software convenzionale per attività quali connettività di rete, gestione dei dispositivi e interfacce utente.

In breve, un singolo FPGA può consolidare funzioni che altrimenti richiederebbero chip di I/O, acceleratori IA, DSP e processori del piano di controllo separati. Il risultato può essere una distinta base ridotta, un ingombro minore della scheda e un consumo energetico inferiore, pur mantenendo la bassa latenza e il determinismo richiesti dalle applicazioni di Edge IA.

L'aggiunta di blocchi tensoriali IA apre nuove possibilità

L'hardware DSP dell'FPGA tradizionale già è adatto a molti carichi di lavoro edge, ma l'inferenza IA tende a essere dominata da operazioni di moltiplicazione-accumulazione dense ma di bassa precisione. Per risolvere questo problema, i dispositivi Agilex 3 e Agilex 5 di Altera sono dotati di DSP potenziato con blocchi tensoriali IA. Si tratta di hardware specializzato per le moltiplicazioni matrice-matrice e vettore-matrice, che appaiono ripetutamente nei grafici di calcolo IA.

Il cuore di questo approccio è un motore di prodotto scalare e di sommatore/accumulatore (Figura 1). In modalità tensore, il motore cablato esegue un prodotto scalare a 10 elementi utilizzando ingressi a 8 bit e pesi precaricati a 8 bit. Per estendere la gamma dinamica, il percorso dati può anche utilizzare un "esponente comune" condiviso per la scalatura a blocchi in stile virgola mobile, affrontando lo scenario tipico in cui l'inferenza IA richiede alta gamma dinamica ma bassa precisione.

Figura 1: Il blocco tensore IA può eseguire prodotti scalari a 10 elementi. (Immagine per gentile concessione di Altera)

Figura 1: Il blocco tensore IA può eseguire prodotti scalari a 10 elementi. (Immagine per gentile concessione di Altera)

Il risultato del prodotto scalare è 32 bit (a virgola fissa o a virgola mobile a precisione singola) e può essere collegato in cascata a uno stadio sommatore/accumulatore aggiuntivo per il calcolo dei prodotti scalari più grandi tra blocchi adiacenti. Ogni blocco tensore IA comprende due colonne di prodotto scalare, consentendo una varietà di modalità operative.

In un caso d'uso tipico, parte dell'hardware matematico potenziato viene utilizzato nel suo ruolo DSP tradizionale, come l'esecuzione di trasformate di Fourier veloci (FFT) su dati radar. Altri sono utilizzati come blocchi tensori IA, come una CNN per eseguire il rilevamento degli oggetti. Questa flessibilità è fondamentale per i sistemi edge che devono gestire l'intelligenza artificiale insieme ad altre funzioni ad alta intensità di calcolo.

Una gamma di opzioni FPGA per carichi di lavoro IA differenti

Le famiglie Agilex offrono anche una notevole flessibilità nella scalabilità delle prestazioni. I componenti vanno da dispositivi incentrati sull'efficienza che misurano appena 12 × 12 mm a varianti ad alte prestazioni che offrono fino a 152,6 tera di operazioni al secondo (TOPS) di picco, con un'analoga scalabilità nelle capacità di interfaccia di memoria e I/O.

Un esempio di componente ad alte prestazioni è Agilex 5 A5ED065BB32AE4SR0, che offre 22,17 TOPS in un contenitore di 32 × 32 mm. Un esempio di componente orientato all'efficienza è Agilex 3 A3CW135BM16AE6S, che fornisce 2,8 TOPS in un contenitore di 16 × 16 mm. Le specifiche chiave di ciascuno di essi sono riportate nella Tabella 1.

|

Tabella 1: Alcune specifiche chiave degli FPGA Agilex 5 e Agilex 3 di esempio. (Tabella per gentile concessione di Altera, modificata dall'autore)

Entrambe le famiglie sono disponibili come FPGA tradizionali o come System-on-Chip (SoC) con processori Arm integrati. I SoC Agilex 3 incorporano un Arm Cortex-A55 dual core a 800 MHz. I SoC Agilex 5 presentano un cluster asimmetrico con due core Cortex-A76 a 1,8 GHz affiancati da due core Cortex-A55 da 1,5 GHz. Entrambe le configurazioni supportano Linux, consentendo lo sviluppo di software convenzionale per connettività di rete, gestione dei dispositivi e interfacce utente.

Semplificare l'implementazione dell'Edge IA con l'uso di FPGA

I modelli di intelligenza artificiale sono tipicamente sviluppati in framework incentrati sul software con cicli di iterazione rapidi, mentre le implementazioni FPGA storicamente richiedono competenze di sviluppo hardware e cicli di integrazione più lunghi. FPGA AI Suite di Altera (Figura 2) offre un percorso più diretto da un modello addestrato a una proprietà intellettuale (IP) di inferenza FPGA distribuibile, utilizzando un flusso compatibile con i tool di AI standard del settore.

Figura 2: Il flusso di lavoro di FPGA AI Suite collega i framework IA standard all'implementazione FPGA. (Immagine per gentile concessione di Altera)

Figura 2: Il flusso di lavoro di FPGA AI Suite collega i framework IA standard all'implementazione FPGA. (Immagine per gentile concessione di Altera)

Il flusso di lavoro può essere riassunto come segue:

- Sviluppare il modello di inferenza in un framework standard come PyTorch, TensorFlow o ONNX.

- Utilizzare il toolkit OpenVINO per convertire il modello in una rappresentazione intermedia (IR) comprendente un file grafico (.xml) e pesi (.bin).

- Passare gli artefatti IR al compilatore FPGA AI Graph, che mappa il modello alle risorse FPGA disponibili. Tali risorse possono includere un processore host esterno, un processore interno o una configurazione senza GUI (headless).

- Compilare e distribuire i livelli risultanti utilizzando Quartus Prime Pro Edition, con l'esecuzione gestita attraverso lo stack runtime del motore di inferenza e le interfacce di programmazione dell'applicazione (API) FPGA AI per il movimento della memoria e la programmazione dell'hardware.

- Come parte del processo di compilazione, utilizzare Architecture Optimizer per bilanciare le prestazioni e l'uso delle risorse. Ad esempio, è possibile utilizzarlo per garantire che l'implementazione soddisfi gli obiettivi di throughput di inferenza, lasciando spazio ad altre logiche FPGA.

In termini pratici, il valore di questo approccio è che trasforma la "distribuzione su un FPGA" in un processo di integrazione piuttosto che in uno sforzo di progettazione dell'acceleratore. I data scientist possono rimanere all'interno di flussi di lavoro consolidati per lo sviluppo di modelli, mentre i team FPGA ed embedded ricevono artefatti che si inseriscono naturalmente in un ciclo build-and-deploy, consentendo un'iterazione più rapida di pari passo con l'evoluzione dei modelli e dei requisiti. I modelli pre-addestrati disponibili attraverso il toolkit Open Model Zoo for OpenVINO possono accelerare ulteriormente lo sviluppo.

Come muovere i primi passi con i kit di sviluppo di facile utilizzo

Per iniziare a esplorare l'Edge IA su FPGA, i progettisti hanno a disposizione diverse opzioni di kit di sviluppo. Per applicazioni con prestazioni più elevate, il kit di sviluppo Atum A5 P0775 di Terasic (Figura 3) è una buona scelta. Costruito attorno al dispositivo Agilex 5 A5ED065BB32AE4SR0, il kit offre un'ampia gamma di interfacce adatte ai sistemi di classe edge. Le caratteristiche principali includono 8 GB di DDR4, porte QSFP+ e porte 2,5 Gbit Ethernet (GbE), 4 PCIe Gen 3, doppi connettori per telecamere MIPI e un'uscita HDMI. Il kit include una licenza gratuita per Quartus Prime Pro Edition.

Figura 3: Il kit di sviluppo Atum A5 P0775 consente di accedere allo sviluppo di IA e visione ad alte prestazioni. (Immagine per gentile concessione di Terasic)

Figura 3: Il kit di sviluppo Atum A5 P0775 consente di accedere allo sviluppo di IA e visione ad alte prestazioni. (Immagine per gentile concessione di Terasic)

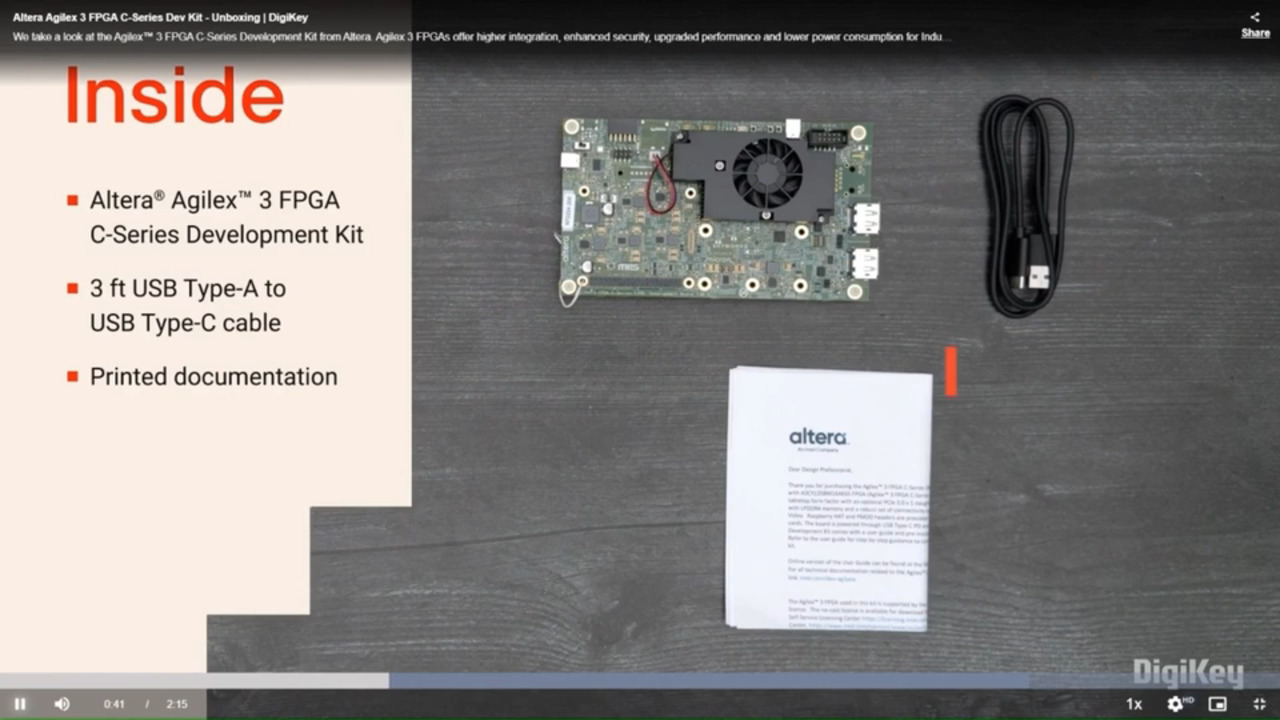

Per le applicazioni incentrate sull'efficienza, i progettisti possono optare per il kit di sviluppo SoC ed FPGA Agilex 3 serie C DK-A3W135BM16AEA (Figura 4). Costruito attorno al dispositivo Agilex 3 A3CW135BM16AE6S, questo kit enfatizza la prototipazione compatta con un'espansione che favorisce l'ecosistema. La scheda offre 4 GB di LPDDR4, GbE, DisplayPort e USB 2.0, oltre a un connettore Raspberry Pi HAT e un'interfaccia Digilent Pmod per un'espansione a basso attrito.

Figura 4: Il kit di sviluppo SoC ed FPGA Agilex 3 serie C DK-A3W135BM16AEA offre una piattaforma compatta per l'Edge IA incentrata sull'efficienza. (Immagine per gentile concessione di Altera)

Figura 4: Il kit di sviluppo SoC ed FPGA Agilex 3 serie C DK-A3W135BM16AEA offre una piattaforma compatta per l'Edge IA incentrata sull'efficienza. (Immagine per gentile concessione di Altera)

Conclusione

L'introduzione di LLM e di altri nuovi carichi di lavoro IA nell'edge sta spingendo gli sviluppatori a cercare nuovi approcci. Gli FPGA offrono una soluzione unica che non solo assicura prestazioni deterministiche a bassa latenza, ma gestisce anche molte altre funzioni di sistema. Con gli FPGA Agilex abilitati all'IA ed FPGA AI Suite, gli sviluppatori possono accedere a queste capacità in modo rapido e semplice, aprendo nuove possibilità architetturali per progetti altamente adattivi e di lunga durata.

Esonero della responsabilità: le opinioni, le convinzioni e i punti di vista espressi dai vari autori e/o dai partecipanti al forum su questo sito Web non riflettono necessariamente le opinioni, le convinzioni e i punti di vista di DigiKey o le sue politiche.