Perché il bus di circuito inter-integrato (I²C) semplifica il collegamento dei circuiti integrati e come utilizzarlo

Contributo di Editori nordamericani di DigiKey

2020-04-07

Per le comunicazioni e il controllo tra i circuiti integrati, non è pratico utilizzare un bus parallelo su una scheda a circuiti stampati. Anche un processore a 8 bit richiederebbe 16 linee solo per i dati e molte altre per un bus di indirizzi. Se poi occorre mettere più circuiti integrati su un bus di comunicazione condiviso, le difficoltà aumentano ulteriormente, perché mancherebbe lo spazio per accogliere tutte quelle tracce sulla scheda. La soluzione è quella di collegare i circuiti integrati utilizzando un bus di comunicazione seriale bifilare come circuito inter-integrato (I2C) che risolve il problema.

Questo articolo descrive le origini del bus I2C e come funziona per fornire un collegamento seriale efficiente tra CI. Spiega quindi come implementare fisicamente il bus I2C, la struttura del protocollo e le applicazioni comuni di questo diffusissimo bus di comunicazioni. A scopo dimostrativo useremo interfacce I2C di esempio e soluzioni di Microchip Technology. Verranno anche illustrate le somiglianze e le differenze di I2C rispetto al System Management Bus (SMBus).

Che cos'è il bus I2C?

Il bus I2C è stato sviluppato da Phillips Semiconductors, ora NXP Semiconductors, nei primi anni '80 come semplice bus bidirezionale bifilare per assicurare comunicazioni efficienti e il controllo dei circuiti integrati su una comune scheda. La prima specifica è stata completata nel 1992 e da allora il bus è diventato uno standard di fatto offerto in componenti di oltre 50 produttori di CI. Quest'ampia diffusione consente un approccio di sistema alla progettazione in cui i circuiti integrati possono essere facilmente inclusi nella struttura del bus I2C senza che sia richiesta una progettazione personalizzata. Diversi altri bus specializzati come SMBus e Power Management Bus (PMBus), e molti altri, condividono l'architettura di base.

Il bus I2C può collegare più CI e sensori perché è indirizzabile: un campo di indirizzo a sette o dieci bit permette al dispositivo master di inviare i messaggi a un dispositivo selezionato. L'I2C originale aveva una velocità di clock massima di 100 kHz, ma nel corso degli anni modalità operative a velocità superiore hanno portato questo limite a 3,4 MHz.

Il bus I2C usa due fili chiamati linea dati seriali, o SDA, e linea di clock seriale, o SCL. SDA e SCL sono linee bidirezionali a drain/collettore aperto, collegate al bus di alimentazione positivo tramite una sorgente di corrente o un resistore di pull-up. Al bus possono essere collegati più dispositivi, con il solo limite della sua capacità elettrica. Il bus è controllato da un dispositivo master e ogni dispositivo sul bus ha un indirizzo univoco. Il dispositivo master può sia trasmettere che ricevere dati sul bus (Figura 1). I2C supporta il funzionamento multi-master con rilevamento delle collisioni e con arbitraggio per evitare che due o più dispositivi master avviino contemporaneamente il trasferimento dei dati. Questo articolo si concentrerà sulle singole configurazioni del master.

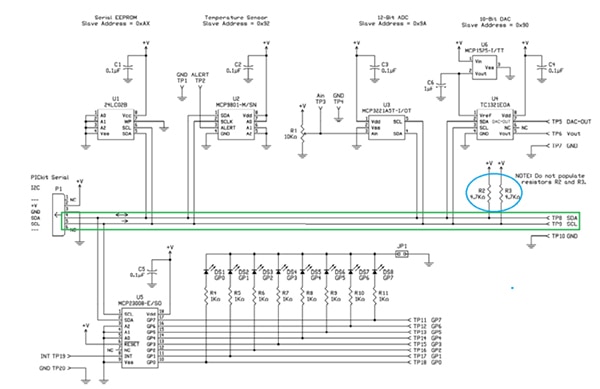

Figura 1: Schema di una scheda dimostrativa di Microchip Technology che implementa il bus I2C e lo collega a cinque diversi dispositivi. Il dispositivo master si trova fuori dalla scheda ed è collegato tramite il connettore P1. Le linee SCL e SDA sono evidenziate in verde e i due resistori di pull-up sono cerchiati in blu. (Immagine per gentile concessione di Microchip Technology)

Figura 1: Schema di una scheda dimostrativa di Microchip Technology che implementa il bus I2C e lo collega a cinque diversi dispositivi. Il dispositivo master si trova fuori dalla scheda ed è collegato tramite il connettore P1. Le linee SCL e SDA sono evidenziate in verde e i due resistori di pull-up sono cerchiati in blu. (Immagine per gentile concessione di Microchip Technology)

La Figura 1 mostra lo schema di una scheda dimostrativa PKSERIAL-I2C1 I2C di Microchip Technology. Questa scheda implementa il bus I2C utilizzando cinque diversi dispositivi, fra cui una EEPROM, un sensore di temperatura, un convertitore analogico/digitale (ADC) a 12 bit, un convertitore digitale/analogico (DAC) a 10 bit e un convertitore seriale/parallelo a 8 bit. Il dispositivo master non si trova sulla scheda ed è collegato tramite il connettore P1. Le linee SCL e SDA del bus sono evidenziate in verde e i resistori di pull-up sono cerchiati in blu.

I livelli SDA e SCL sono, in genere, una percentuale fissa della tensione di alimentazione positiva, solitamente indicata come VDD. I livelli di riferimento sono fissati al 70% e al 30% di VDD rispettivamente per la logica "1" (alto) e la logica "0" (basso).

I segnali di clock avvengono per burst con un clock per ogni bit di dati trasferiti. I dati sulla linea SDA devono essere validi mentre il clock è alto e possono essere cambiati solo quando il clock è basso.

Dal punto di vista progettuale, i nuovi progetti sono semplificati perché le interfacce I2C sono integrate nei CI e non occorre progettarle. Ogni dispositivo si collega direttamente al bus. I circuiti integrati possono essere aggiunti o rimossi dal bus senza che ciò incida sugli altri circuiti (supponendo che il numero totale di circuiti integrati non superi il limite di capacità). Il semplice bus bifilare riduce al minimo il numero di pin su ogni CI e il numero di piste sulla scheda.

Il protocollo I2C

Il bus è basato su 8 bit e comunica in byte. Come ricordato sopra, la frequenza di clock massima originale era di 100 kHz in quella che ora viene detta modalità standard. Il bus oggi supporta 400 kbit/s in modalità veloce, fino a 1 Mbit/s in modalità ultra veloce e fino a 3,4 Mbit/s in modalità alta velocità (Hs-Mode).

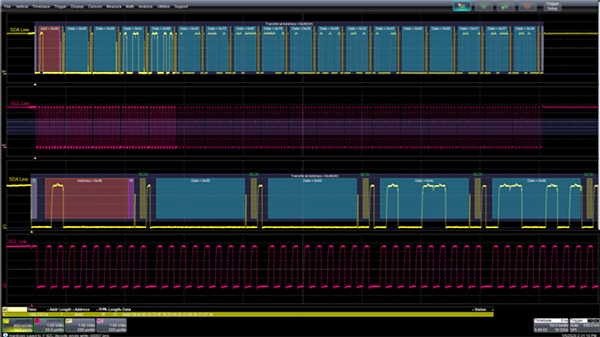

Per illustrare il protocollo I2C è più semplice dare uno sguardo a un tipico trasferimento sul bus (Figura 2). La fonte dell'immagine visualizzata è un oscilloscopio di Teledyne LeCroy con trigger di dati seriali a bassa velocità e opzione di decodifica: WS4KHD-EMB TD. Questo oscilloscopio può attivare e decodificare fino a 19 interfacce dati seriali a bassa velocità, compreso I2C.

Figura 2: Un tipico pacchetto dati I2C composto da un bit di start, campo di indirizzo, bit di conferma, 17 byte di dati, ognuno con il proprio bit ACK, e un bit di stop. Ogni campo è identificato da un overlay con codifica a colori. La traccia superiore (gialla) è l'intero pacchetto SDA, sotto di essa c'è il clock SCL (rosso). La terza e la quarta traccia sono viste ingrandite orizzontalmente di entrambi i segnali. (Immagine per gentile concessione di DigiKey)

Figura 2: Un tipico pacchetto dati I2C composto da un bit di start, campo di indirizzo, bit di conferma, 17 byte di dati, ognuno con il proprio bit ACK, e un bit di stop. Ogni campo è identificato da un overlay con codifica a colori. La traccia superiore (gialla) è l'intero pacchetto SDA, sotto di essa c'è il clock SCL (rosso). La terza e la quarta traccia sono viste ingrandite orizzontalmente di entrambi i segnali. (Immagine per gentile concessione di DigiKey)

Il trigger dell'oscilloscopio si attiva su specifici eventi seriali, tra cui start, stop, mancata conferma (ACK), indirizzo, dati, indirizzo più dati, lunghezza del frame e trasferimento dati della EEPROM. Gli elementi del protocollo dello standard di dati seriali sono identificati da un overlay con codifica a colori. Ogni campo del protocollo viene decodificato in binario, esadecimale o ASCII e il codice selezionato è visualizzato all'interno dell'overlay.

Il segnale SDA appare come una traccia gialla, mentre il segnale SCL viene mostrato come una traccia rossa. La casella di overlay grigia indica le funzioni di avvio e di arresto. L'overlay rosso mattone denota i dati dell'indirizzo, il campo blu riguarda i dati del pacchetto e le caselle di overlay color oliva denotano le funzioni ACK.

La traccia superiore mostra l'intero pacchetto SDA I2C dall'avvio all'arresto. Subito sotto vi è il segnale SCL corrispondente. La terza traccia in basso è una traccia di zoom esteso nel tempo del segnale SDA, e sotto vi è il segnale SCL sincrono.

Sia la linea SDA che quella SCL rimangono nello stato alto tra un trasferimento e l'altro quando il bus è libero. Il segnale SCL è costituito da burst di nove impulsi alla frequenza di clock, uno per ogni bit di dati trasferito e uno supplementare per il bit ACK.

Tutte le transazioni del bus iniziano con un bit di start generato dal master indicato nella traccia SDA ingrandita come una casella di overlay di colore grigio. Lo start è indicato dal master che abbassa la linea SDA mentre la linea SCL è in stato alto. Una volta che il master ha emesso il bit di start, il bus è considerato occupato. Il master può emettere più start; in questa situazione gli start successivi spesso sono detti restart.

Tutti i trasferimenti di dati hanno una lunghezza di 8 bit (un byte), ognuno dei quali è seguito da un bit ACK. I bit vengono trasmessi partendo da quello più significativo (MSB). Ogni trasferimento di byte deve essere confermato. Se il dispositivo slave è occupato e non può ricevere o trasmettere dati, può abbassare la linea SCL. Il dispositivo master verrà così forzato in uno stato di attesa fino a quando il dispositivo slave non rilascia la linea SCL.

Il bit ACK si forma dopo che il dispositivo trasmittente ha rilasciato la linea SDA prima del nono impulso di clock di conferma. Se il dispositivo ricevente ha ricevuto il byte di dati, abbassa la linea SDA. Nella vista ingrandita dell'SDA riportata nella Figura 2, c'è un picco transitorio piccolo subito prima del nono impulso di clock: segnala il rilascio della linea SDA che torna allo stato alto. Il ricevitore abbassa la linea SDA generando il segnale ACK, che è contrassegnato simbolicamente dall'overlay della casella color oliva. Se non la abbassa prima del nono impulso di clock, si tratta di una risposta di non conferma (NACK). In caso di NACK, il master può generare un segnale di stop e interrompere il trasferimento oppure emettere un segnale ripetuto di start per riprovare.

Subito dopo la condizione di avvio, viene rilasciato un indirizzo slave. È indicato da una casella di overlay di colore rosso mattone. Esistono due possibili formati di indirizzo: a 7 e a 10 bit. L'indirizzo a 7 bit è quello più comune. I primi 7 bit dopo l'avvio rappresentano i dati dell'indirizzo. L'8o bit indica la direzione dei dati: lettura o scrittura. In caso di scrittura, la linea SDA è in uno stato basso, mentre in caso di lettura è in uno stato alto. L'indirizzamento a 10 bit utilizza i primi due byte dopo la condizione di avvio. I2C riserva diversi indirizzi per le funzioni interne. I dati dell'indirizzo di decodifica vengono visualizzati nella casella di overlay dell'indirizzo in formato binario, esadecimale o ASCII.

I campi di overlay blu contrassegnano i trasferimenti di dati. Ognuno è lungo otto bit ed è seguito da una risposta ACK/NACK. Il numero di byte di dati in un pacchetto I2C è illimitato (la Figura 2 ne mostra 17). I dati decodificati, come la decodifica dell'indirizzo, appaiono nella casella di overlay dei dati. Il flusso di dati è seguito da un bit di stop generato dal master alla fine del trasferimento dati, indicato da una casella di overlay grigia nella traccia dei dati in alto. Il bit di stop è una transizione da basso ad alto sulla linea SDA mentre la linea SCL è in stato alto. Dopo il segnale di stop, il bus è di nuovo libero.

La tabella nella parte inferiore del display riassume tutte le informazioni sul relativo pacchetto di dati, compreso il tempo trascorso dal trigger, la lunghezza dell'indirizzo, l'indirizzo, l'operazione di lettura o scrittura, la lunghezza del pacchetto e un riepilogo del contenuto dei dati. Il numero di voci nella tabella corrisponde al numero di pacchetti I2C acquisiti dal campo di applicazione, che in questo caso è solo una linea singola.

Se si verifica un errore di protocollo, viene segnalato da una casella di colore rosso acceso dietro le altre caselle di overlay del protocollo.

Dispositivi I2C

Uno dei maggiori vantaggi del bus I2C è il numero molto grande di dispositivi che l'hanno incorporato nel proprio progetto. La scheda dimostrativa di Microchip Technologies fornisce alcuni esempi dei tipi di circuiti integrati che incorporano il bus I2C o uno dei suoi derivati come SMBus.

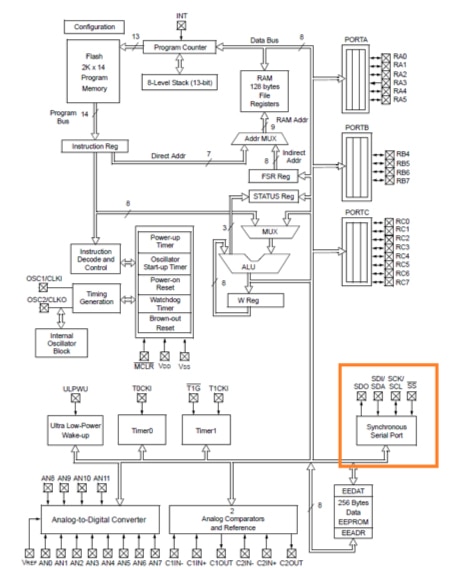

PIC16F677 di Microchip Technology è un microcontroller a 8 bit usato in numerosi progetti embedded. Implementa una porta seriale sincrona che può essere controllata per comunicare con l'interfaccia periferica seriale (SPI) o I2C con altri controller o dispositivi periferici (Figura 3).

Figura 3: PIC16F677 di Microchip Technology è un microcontroller a 8 bit che include una porta seriale sincrona (evidenziata in arancione) in grado di essere programmata come bus SPI o I2C. (Immagine per gentile concessione di Microchip Technology)

Figura 3: PIC16F677 di Microchip Technology è un microcontroller a 8 bit che include una porta seriale sincrona (evidenziata in arancione) in grado di essere programmata come bus SPI o I2C. (Immagine per gentile concessione di Microchip Technology)

Questo microcontroller supporta la modalità sia master che slave di I2C utilizzando l'indirizzamento a 7 o 10 bit. Usa il pin SCK/SCL per il segnale di clock SCL2C e il pin SDI/SDA per il segnale dei dati.

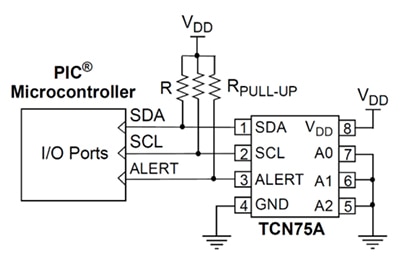

Questi due pin sono collegati alle linee SCL e SDA sul bus I2C per consentire le comunicazioni con altri dispositivi. Una connessione comune è quella con un sensore basato su I2C come il sensore di temperatura seriale bifilare TCN75AVOA713 di Microchip Technology (Figura 4).

Figura 4: Il sensore di temperatura TCN75A di Microchip Technology è direttamente collegato al microcontroller PIC16F677 per comunicare i dati della temperatura. (Immagine per gentile concessione di Microchip Technology)

Figura 4: Il sensore di temperatura TCN75A di Microchip Technology è direttamente collegato al microcontroller PIC16F677 per comunicare i dati della temperatura. (Immagine per gentile concessione di Microchip Technology)

Avendo capacità di comunicazione seriale, questo sensore di temperatura ha maggiori funzionalità. I suoi registri interni programmabili dall'utente possono essere usati per impostare la risoluzione di misurazione, la modalità di spegnimento per il risparmio energetico e anche l'uscita di allarme per segnalare quando l'intervallo di temperatura supera i limiti preimpostati.

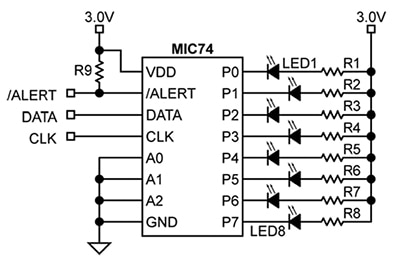

Esistono anche diversi dispositivi che decodificano il flusso di dati seriali I2C e li scompongono in dati paralleli. Prendiamo in esame l'espansore di I/O bifilare MIC74YQS-TR di Microchip Technology e il controller della ventola (Figura 5).

Figura 5: L'espansore di I/O MIC74YQS-TR di Microchip Technology converte il flusso di dati seriali in otto linee di I/O parallele indipendenti. (Immagine per gentile concessione di Microchip Technology)

Figura 5: L'espansore di I/O MIC74YQS-TR di Microchip Technology converte il flusso di dati seriali in otto linee di I/O parallele indipendenti. (Immagine per gentile concessione di Microchip Technology)

Questo CI è un espansore di I/O completamente programmabile che fornisce otto linee I/O indipendenti. Le linee I/O possono essere programmate individualmente come ingresso o uscita. La Figura 5 mostra MIC74YQS-TR che pilota otto LED sotto il controllo del bus seriale. È simile all'uso di MCO23008 nella scheda dimostrativa I2C riportata nella Figura 1. MIC74YQS-TR, in combinazione con un regolatore di potenza, può anche implementare un comando di velocità del motore di una ventola utilizzando i quattro bit più significativi.

SMBus e I2C

L'ingresso seriale all'espansore di I/O è progettato per SMBus, ma è compatibile anche con il bus I2C. La specifica SMBus si basa su I2C ed è stata definita da Intel e Duracell nel 1994. La differenza principale è data dal fatto che i livelli della logica I2C in modalità standard sono relativi rispetto a VDD e quelli di SMBus sono fissi. Nella maggior parte dei casi, con VDD tra 3 e 5 V, l'esperienza ha dimostrato che questo non rappresenta un problema.

Un'altra differenza è che SMBus è limitato a frequenze di clock di 100 kHz o inferiori, mentre I2C ha diverse modalità che supportano frequenze di clock superiori. Per quanto riguarda la compatibilità del bus, questo limita la velocità massima di clock a 100 kHz o alla modalità di clock standard di I2C.

Pertanto, salvo in situazioni molto speciali, SMBus e I2C sono compatibili.

Conclusione

Il bus I2C e i suoi derivati sono diffusi in centinaia di circuiti integrati di ogni tipo, semplificandone la connessione in applicazioni e progetti variegati. L'accoppiamento di sensori a segnale misto e analogici amplia la capacità dei sistemi embedded basati su microcontroller. Tutto questo con una semplice interfaccia digitale seriale bifilare.

Esonero della responsabilità: le opinioni, le convinzioni e i punti di vista espressi dai vari autori e/o dai partecipanti al forum su questo sito Web non riflettono necessariamente le opinioni, le convinzioni e i punti di vista di DigiKey o le sue politiche.