Usare un singolo processore HMP a bassa potenza per carichi di elaborazione in tempo reale e per le applicazioni.

Contributo di Editori nordamericani di DigiKey

2019-08-06

I consumatori si aspettano che i dispositivi elettronici personali e mobili rispondano più rapidamente, siano dotati di maggiori funzionalità, ma anche che le loro batterie durino più a lungo. Per gli sviluppatori, tuttavia, i requisiti di risposta in tempo reale e di prestazioni elevate per molte applicazioni hanno comportato inevitabilmente l'uso di processori separati per soddisfare queste richieste in conflitto. Ma questo aumenta i costi, il consumo e lo spazio, nonché il layout dell'hardware e la complessità del software.

Un approccio migliore sarebbe quello di integrare l'hardware richiesto in un unico chip. Entriamo nel mondo dei dispositivi di elaborazione multicore eterogenea (HMP). Dato che contengono più core di diversi tipi, questi processori possono offrire vantaggi in termini di ottimizzazione delle prestazioni, riduzione del consumo energetico e maggiore sicurezza e affidabilità del sistema.

Questo articolo descrive come gli sviluppatori possono utilizzare un processore multicore eterogeneo di NXP Semiconductors per soddisfare la domanda di carichi di lavoro misti senza compromettere i requisiti di basso consumo e ridotta complessità di progettazione.

Requisiti che cambiano

I progressi compiuti in materia di tecnologia dei sensori e algoritmi di elaborazione dei dati hanno creato per gli sviluppatori importanti opportunità di gestire le esigenze contrastanti dell'acquisizione dati in tempo reale e dell'esecuzione di algoritmi ad alta intensità di calcolo. In passato, gli sviluppatori suddividevano in genere questi carichi di lavoro in sistemi separati.

Al livello più basso della gerarchia di rete, processori integrati come quelli basati sul core Arm® Cortex®-M4 raccoglierebbero i dati, eseguendo codice ottimizzato in un sistema operativo in tempo reale (RTOS) o in un sistema bare-metal. A un livello gerarchicamente superiore, processori di applicazioni ad alte prestazioni come quelli basati sul core Arm Cortex-A7 eseguirebbero a loro volta algoritmi di analisi dei dati, eseguendo il codice applicativo su sistemi operativi molto diffusi come Linux o Android.

L'avvento dei sistemi di edge computing ha avvicinato l'esecuzione del codice dell'applicazione alla sorgente dei dati. Ora, la richiesta di una risposta più rapida da algoritmi di analisi più complessi ha spinto di fatto i requisiti di elaborazione delle applicazioni nei dispositivi finali. I consumatori si aspettano sempre più che in dispositivi come sensori di Internet delle cose (IoT), dispositivi indossabili e altri prodotti a basso consumo siano integrate sofisticate capacità di analisi, compresi i metodi basati sull'intelligenza artificiale.

Il ruolo dell'elaborazione multicore eterogenea

L'emergere di dispositivi HMP che combinano core di processore delle applicazioni ed embedded ha aiutato gli sviluppatori a gestire con maggiore efficienza carichi di lavoro misti in numerose applicazioni. I processori HMP integrano core diversi, ognuno dei quali è ottimizzato per soddisfare i vari requisiti associati al carico di lavoro del prodotto target. Con la famiglia di processori (a bassissima potenza) i.MX 7ULP di NXP, gli sviluppatori possono sfruttare le capacità prestazionali di un'architettura HMP per soddisfare i consumatori che pretendono alte prestazioni e una batteria di lunga durata nei prodotti ULP di ultima generazione.

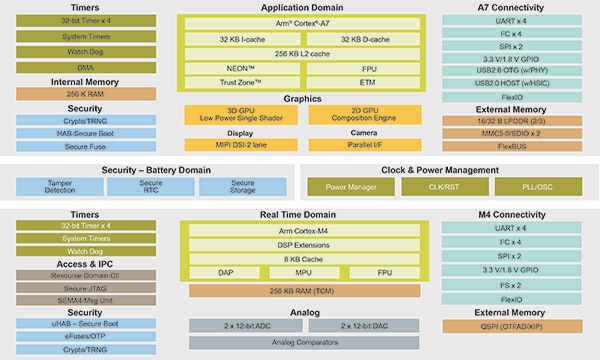

Disponibili sia nella versione consumer (MCIMX7U5DVP07SC) che in quella industriale (MCIMX7U5CVP06SC), i processori i.MX 7ULP integrano core eterogenei con unità di elaborazione grafica, acceleratori di sicurezza, controller di memoria e una serie completa di interfacce periferiche (Figura 1).

Figura 1: Oltre al ricco corredo di moduli e periferiche, la famiglia di processori per applicazioni i.MX 7ULP di NXP combina un core Arm Cortex-M4 per l'elaborazione in tempo reale con un core Arm Cortex-A7 per l'elaborazione delle applicazioni. Usa domini della potenza separati per ottimizzare consumi e prestazioni. (Immagine per gentile concessione di NXP)

Figura 1: Oltre al ricco corredo di moduli e periferiche, la famiglia di processori per applicazioni i.MX 7ULP di NXP combina un core Arm Cortex-M4 per l'elaborazione in tempo reale con un core Arm Cortex-A7 per l'elaborazione delle applicazioni. Usa domini della potenza separati per ottimizzare consumi e prestazioni. (Immagine per gentile concessione di NXP)

Progettata espressamente per i progetti di dispositivi portatili vincolate dai consumi, la famiglia i.MX 7ULP di NXP risponde ai requisiti emergenti combinando un core Arm Cortex-A7 con un core Cortex-M4, alimentati ognuno da un dominio della potenza separato. Inoltre, l'uso di isole di alimentazione diverse consente di spegnere selettivamente i diversi moduli quando non servono. Come descritto sotto, le sofisticate funzionalità di gestione energetica integrate nei dispositivi i.MX 7ULP consentono agli sviluppatori di utilizzare queste isole e questi domini della potenza per ottimizzare le prestazioni e il consumo in base alle applicazioni.

Ottimizzazione della potenza

Quando ha progettato la famiglia i.MX 7ULP, NXP ha integrato nei dispositivi funzionalità di ottimizzazione della potenza e delle prestazioni a partire dalla progettazione del chip, estendendola via via a tutta l'architettura.

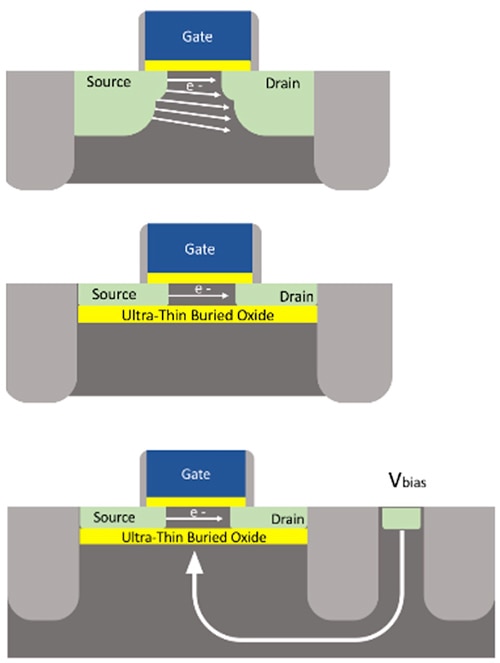

Al livello più fondamentale, la famiglia i.MX 7ULP combina metodi di fabbricazione che riducono la corrente di dispersione con geometrie di transistor che diminuiscono le correnti parassite, abbassando di conseguenza il consumo dinamico di energia. Diversamente dalle strutture a transistor convenzionali (Figura 2, in alto), i dispositivi i.MX 7ULP sono fabbricati con uno strato isolante ultrasottile denominato Buried Oxide (ossido sepolto) (Figura 2, al centro) che riduce il flusso di elettroni dalla sorgente al drain, diminuendo in tal modo la corrente di dispersione. Un ulteriore miglioramento consente ai progettisti di aggiungere la polarizzazione positiva (FBB) o la polarizzazione mediante resistenze RB (RBB) (Figura 2, in basso).

Figura 2: Un transistor convenzionale può presentare una notevole dispersione quando gli elettroni scorrono dalla sorgente al drain (in alto), ma la famiglia i.MX 7ULP di NXP è fabbricata con uno strato isolante ultrasottile denominato Buried Oxide (ossido sepolto) che ostacola il flusso di elettroni (al centro), e con una struttura che lo accelera o lo rallenta con polarizzazione positiva (FBB) o con quella mediante resistenze RB (RBB) (in basso). (Immagine per gentile concessione di NXP)

Figura 2: Un transistor convenzionale può presentare una notevole dispersione quando gli elettroni scorrono dalla sorgente al drain (in alto), ma la famiglia i.MX 7ULP di NXP è fabbricata con uno strato isolante ultrasottile denominato Buried Oxide (ossido sepolto) che ostacola il flusso di elettroni (al centro), e con una struttura che lo accelera o lo rallenta con polarizzazione positiva (FBB) o con quella mediante resistenze RB (RBB) (in basso). (Immagine per gentile concessione di NXP)

Quando fra le massime priorità vi è l'efficienza energetica, gli sviluppatori possono usare l'RBB per ridurre il flusso di elettroni, la corrente di dispersione e i consumi complessivi del dispositivo, a discapito delle prestazioni. Per contro, se vogliono migliorare le prestazioni possono utilizzare l'FBB per aumentare il flusso di elettroni, ma così facendo si aumenta la corrente di dispersione e quindi il consumo energetico.

A livello di progettazione del chip, la famiglia i.MX 7ULP incorpora più tecniche tra cui il controllo dinamico della frequenza (DFS) e il controllo dinamico della tensione (DVS), il clock gating e il power gating basati sul software. Oltre a ridurre il consumo energetico di diverse periferiche, gli sviluppatori possono utilizzare queste funzionalità per spegnere selettivamente blocchi di memoria interna o per mettere la memoria in diverse modalità di risparmio energetico.

A livello di architettura, la capacità di ottimizzare consumi e prestazioni viene ulteriormente estesa con l'uso di più domini della potenza, inclusi quelli separati, come si è visto prima, per i sottosistemi Cortex-A7 e Cortex-M4.

Ognuno dei domini della potenza del core del processore include driver FBB e RBB, regolatori a bassa caduta di tensione (LDO) dedicati e monitor del rilevatore di alto livello (HVD) e del rilevatore di basso livello (LVD) progettati per segnalare escursioni di alimentazione al di sopra o al di sotto delle soglie specificate. Un monitor di reset all'accensione (PoR) separato rileva il livello di tensione nel dominio della potenza sempre in funzione.

Oltre ai domini della potenza separati dei core, quelli singoli controllano anche funzioni del sistema come hardware sempre in funzione, mentre un dominio alimentato a batteria gestisce l'alimentazione a funzioni critiche tra cui il clock in tempo reale e un modulo di archiviazione non volatile sicuro. Come per quelli del core, ognuno di questi domini della potenza specializzati supporta una serie completa di funzioni specializzate di risparmio energetico (che sono troppe per poter essere trattate una ad una in un unico articolo).

Per fare un solo esempio, il dominio della potenza per la funzionalità sempre in funzione include un modulo LLWU (unità di riattivazione a bassa dispersione) che consente agli sviluppatori di utilizzare più pin esterni o moduli interni come sorgente di riattivazione per le speciali modalità di alimentazione a bassa dispersione descritte sotto.

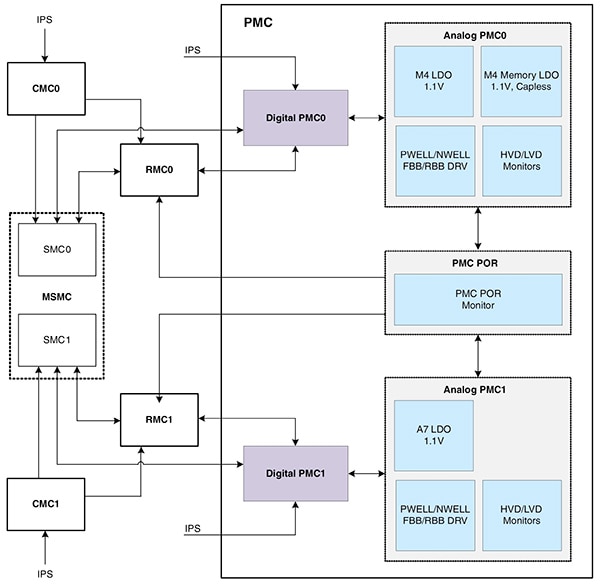

Queste caratteristiche architettoniche sono collegate assieme nel controller di gestione energetica (PMC) integrato del dispositivo, che gestisce queste isole e questi domini della potenza separati del dispositivo (Figura 3).

Figura 3: La famiglia i.MX 7ULP di NXP integra una sofisticata capacità di controllo che consente agli sviluppatori di configurare in modo programmatico isole e domini della potenza per ottimizzare consumi e prestazioni al fine di soddisfare i mutevoli requisiti delle applicazioni. (Immagine per gentile concessione di NXP)

Figura 3: La famiglia i.MX 7ULP di NXP integra una sofisticata capacità di controllo che consente agli sviluppatori di configurare in modo programmatico isole e domini della potenza per ottimizzare consumi e prestazioni al fine di soddisfare i mutevoli requisiti delle applicazioni. (Immagine per gentile concessione di NXP)

Seguendo questo approccio, gli sviluppatori avviano le transizioni in modalità di alimentazione inviando i comandi attraverso il normale bus del sottosistema periferico intelligente (IPS) a un insieme di controlli che comprende tre moduli strettamente accoppiati:

- Core Mode Controller (CMC), che supporta funzioni di più core

- Multicore System Mode Controller (MSMC), comprendente System Mode Controller 0 (SMC0) per il dominio della potenza Cortex-M4 e SMC1 per il dominio della potenza Cortex-A7, che gestisce il sequenziamento tra le diverse modalità di alimentazione, monitora gli eventi utilizzati per avviare le transizioni della modalità di alimentazione e, in genere, controlla le funzioni di alimentazione, clock e memoria associate all'ottimizzazione dell'alimentazione

- Reset Mode Controller (RMC), che gestisce le funzioni di reset del chip

Ottimizzazione di potenza e prestazioni

Grazie a tutte le sue capacità di gestione energetica, la famiglia i.MX 7ULP presenta un modello di programmazione che gli sviluppatori conoscono molto bene. Come nel caso di altri processori avanzati, i dispositivi i.MX 7ULP raggiungono diversi stati operativi a bassa potenza attraverso una serie di modalità programmabili. I core del processore i.MX 7ULP supportano diverse modalità di bassa potenza controllate da software che consentono agli sviluppatori di ridurre il consumo energetico al livello più basso possibile, secondo la funzionalità richiesta.

Utilizzando queste modalità, possono impostare uno o entrambi i core e i loro sottosistemi in diverse varianti di una normale modalità RUN, WAIT e STOP.

La normale modalità RUN e quella HSRUN ad alta velocità assicurano un funzionamento ad alte prestazioni per supportare le parti di un'applicazione che richiedono molti calcoli. In modalità HSRUN, il sottosistema core opera alla massima frequenza. Se l'applicazione è in grado di tollerare prestazioni inferiori, gli sviluppatori possono impostare il core in modalità VLPR per il funzionamento a una frequenza massima di 48 MHz, con un consumo energetico ovviamente inferiore.

Nella normale modalità WAIT, le periferiche sono completamente funzionanti ma il core è gestito tramite il clock gating: in attesa in uno stato statico ma pronto a riattivarsi alla ricezione di un segnale WFI (Wait-For-Interrupt). Con questa modalità, gli sviluppatori possono consentire alle operazioni periferiche autonome di riempire i buffer, oppure utilizzare le transazioni di accesso alla memoria diretta (DMA) per riempire la memoria di sistema prima di emettere un interrupt che toglie il core dallo stato WAIT. La modalità VLPW consente alle periferiche di continuare le operazioni a frequenza ridotta ma riduce la frequenza dei clock del core al valore minimo necessario per l'applicazione corrente.

In applicazioni come i dispositivi indossabili o portatili, il sistema potrebbe avere lunghi periodi di inattività, intervallati da sporadiche riprese. In questi casi, la capacità di risparmiare energia è fondamentale per la durata della batteria. Quando l'applicazione può tollerare un tempo di riattivazione più lento per il core, la possibilità di mettere il dispositivo in stati di sospensione ancora più profondi rispetto a RUN, WAIT o variazioni molto basse dei consumi offre un'opzione particolarmente efficace. A sostegno di questo approccio, gli sviluppatori possono mettere ogni sottosistema core i.MX 7ULP in uno stato di sospensione più profondo che comporta tempi diversi di riattivazione:

- In stato STOP, alcune periferiche possono funzionare in modo asincrono ma il core rimane in uno stato statico con tempi di riattivazione di 7 μs per Cortex-A7 o di 7 μs per Cortex-M4

- Nella modalità VLPS, le operazioni periferiche sono ulteriormente limitate ma il core rimane in uno stato statico con tempi di riattivazione di 21,5 μs (Cortex-A7) o di 9 μs (Cortex-M4).

Se le applicazioni hanno requisiti di alimentazione ancora più rigorosi, gli sviluppatori possono impostare ogni core nelle seguenti modalità speciali a bassa dispersione che arrestano più sottosistemi del dispositivo:

- Modalità LLS, che riduce la frequenza del clock del core, del bus e delle periferiche, lasciando il core in uno stato WFI, con un conseguente tempo di riattivazione di 40 μs (Cortex-A7) o di 58 μs (Cortex-M4)

- Modalità VLLS, che riduce la frequenza del clock dell'intero dominio della potenza del core, con conseguenti tempi di riattivazione più lunghi, compresi i 60 μs per Cortex-A7 o i 375 μs per Cortex-M4

Per risparmi energetici ancora maggiori, gli sviluppatori possono utilizzare l'RBB in alcune modalità di alimentazione, comprese quelle VLPS e LLS, con una corrispondente riduzione delle prestazioni e un aumento incrementale del tempo di riattivazione tra 2 e 4 μs circa.

Quando invece è necessario gestire carichi di lavoro ad alta intensità di calcoli, possono eseguire i core in una speciale modalità di esecuzione ad alta velocità (HSRUN). La modalità HSRUN sposta il core Cortex-A7 dalla normale frequenza operativa di 500 MHz a una di sovrapilotaggio a 720 MHz.

Grazie a questo eccellente livello di controllo, gli sviluppatori possono configurare i.MX 7ULP per soddisfare requisiti di alimentazione anche molto spinti, senza sacrificare le funzionalità essenziali. Ad esempio, un'applicazione potrebbe aver bisogno del minor consumo energetico possibile, ma richiedere la funzionalità in tempo reale del core Cortex-M4, oltre all'uso di memoria o periferiche specifiche del sottosistema Cortex-A7. In questo caso, lo sviluppatore può mettere il sottosistema Cortex-A7 nello stato STOP o VLPS, accedendo alla sua memoria o alle sue periferiche da Cortex-M4 mentre quel core esegue le sue operazioni in tempo reale. Per aumentare i risparmi energetici, può utilizzare il clock del Cortex-M4 per pilotare le periferiche del Cortex-A7.

Implementazione semplice del sistema

Per implementare un sistema a bassa potenza con i.MX 7ULP e soddisfare i requisiti di consumo e prestazioni, gli sviluppatori possono scegliere tra le configurazioni e le modalità di alimentazione programmabili tramite software che sono disponibili. Per quanto riguarda l'hardware, la progettazione del sistema è ancora più semplice.

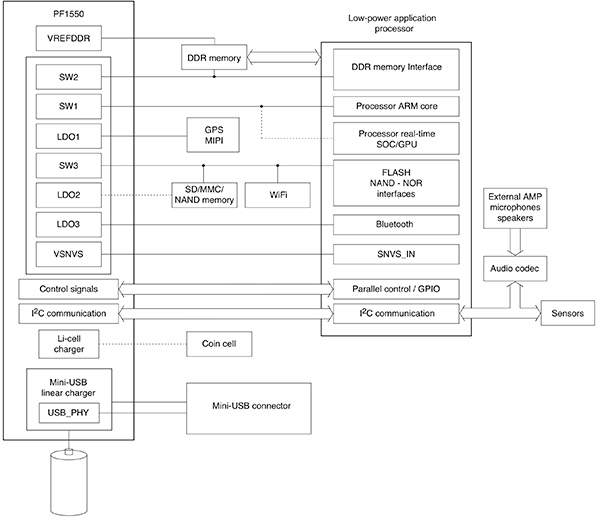

Per le applicazioni tipiche, possono semplicemente combinare un processore i.MX 7ULP con il corrispondente CI di gestione energetica (PMIC) MC32PF1550A3EPR2 di NXP per realizzare un progetto in grado di gestire carichi di lavoro misti senza compromettere la limitata potenza disponibile (Figura 4).

Figura 4: Il CI di gestione energetica MC32PF1550A3EPR2 di NXP offre tutte le sorgenti di alimentazione richieste dal processore i.MX 7ULP di NXP, riducendo la progettazione hardware a una semplice combinazione di questi due dispositivi e a pochi componenti passivi. (Immagine per gentile concessione di NXP)

Figura 4: Il CI di gestione energetica MC32PF1550A3EPR2 di NXP offre tutte le sorgenti di alimentazione richieste dal processore i.MX 7ULP di NXP, riducendo la progettazione hardware a una semplice combinazione di questi due dispositivi e a pochi componenti passivi. (Immagine per gentile concessione di NXP)

Progettato espressamente per supportare i requisiti di alimentazione dei processori NXP, ad esempio della famiglia i.MX 7ULP, MC32PF1550A3EPR2 integra tre regolatori buck a modalità commutata (SW1, SW2, SW3), tre regolatori LDO (LDO1, LDO2, LDO3), una sorgente di tensione di riferimento della memoria, un caricatore completo di batterie al litio a cella singola e memoria a programmazione unica (OTP) per la configurazione del dispositivo.

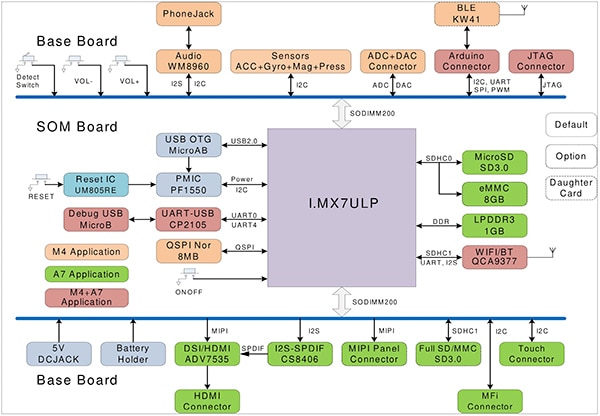

Con il suo kit di valutazione MCIMX7ULP-EVK, NXP dimostra l'interfaccia hardware semplice richiesta per combinare il PMIC MC32PF1550A3EPR2 e il dispositivo i.MX 7ULP. Oltre a una scheda System-on-Module (SoM) che contiene il processore i.MX 7ULP e il PMIC MC32PF1550A3EPR2, il kit include una scheda base con diversi sensori, capacità wireless, un codec audio, un connettore SD e diversi altri connettori, compresi JTAG e Arduino (Figura 5).

Figura 5: Il kit di valutazione MCIMX7ULP-EVK combina una scheda System-on-Module (SoM) che contiene un processore i.MX 7ULP e un PMIC MC32PF1550A3EPR2 con una scheda base che contiene sensori, connettori e altri componenti richiesti per accelerare lo sviluppo software con i dispositivi i.MX 7ULP. (Immagine per gentile concessione di NXP)

Figura 5: Il kit di valutazione MCIMX7ULP-EVK combina una scheda System-on-Module (SoM) che contiene un processore i.MX 7ULP e un PMIC MC32PF1550A3EPR2 con una scheda base che contiene sensori, connettori e altri componenti richiesti per accelerare lo sviluppo software con i dispositivi i.MX 7ULP. (Immagine per gentile concessione di NXP)

Il kit di valutazione fornisce funzionalità predefinite, ma NXP offre agli sviluppatori anche file di progettazione, strumenti e BSP (Board Support Package) scaricabili per software personalizzato che utilizza FreeRTOS per il codice in tempo reale e Linux o Android per il codice delle applicazioni.

Conclusione

La richiesta di prodotti mobili con funzionalità più sofisticate e con una maggiore durata della batteria costringeva di solito gli sviluppatori a scendere a compromessi tra consumi e prestazioni. Inoltre, le crescenti aspettative di un invio tempestivo dei dati dai vari sensori di dispositivi IoT indossabili e di altri prodotti portatili hanno costretto a ulteriori compromessi tra capacità in tempo reale e prestazioni a livello di applicazioni.

Come è stato però dimostrato, per soddisfare i rigorosi requisiti di bassissimo consumo senza sacrificare le capacità, gli sviluppatori possono ricorrere ad architetture HMP come quelle utilizzate nella famiglia di processori i.MX 7ULP di NXP.

Esonero della responsabilità: le opinioni, le convinzioni e i punti di vista espressi dai vari autori e/o dai partecipanti al forum su questo sito Web non riflettono necessariamente le opinioni, le convinzioni e i punti di vista di DigiKey o le sue politiche.