Nozioni di base sui sintetizzatori di frequenza con circuito ad aggancio di fase

Contributo di Editori nordamericani di DigiKey

2021-02-03

L'aumento della velocità dati nei bus di comunicazione seriale ad alta velocità richiede clock di sistema con frequenze più alte, stabilità superiore, maggiore risoluzione e maggiore purezza del segnale. I sintetizzatori digitali diretti offrono queste caratteristiche ma solo a frequenze inferiori a 2 o 3 GHz. Serve una soluzione per le frequenze fino a decine di gigahertz.

Questa soluzione inizia dai sintetizzatori di frequenza analogici basati sul circuito ad aggancio di fase (PLL), che generano frequenze di clock fino a 30 GHz. Quindi, i sintetizzatori a N intero (che moltiplicano la frequenza di riferimento di un valore intero) e i sintetizzatori a N frazionario (che moltiplicano la frequenza di riferimento di valori frazionari non interi) impiegano tecniche speciali che riducono al minimo il rumore di fase e altre impurità del segnale.

Questo articolo descrive la progettazione di sintetizzatori di frequenza a N intero e frazionario utilizzando dispositivi di esempio di Analog Devices. L'articolo evidenzia anche le innovazioni che permettono a questi dispositivi di essere utilizzati per collegamenti di dati seriali ad alta velocità e i per radar agili in frequenza.

Sintetizzatori a N intero con circuito ad aggancio di fase

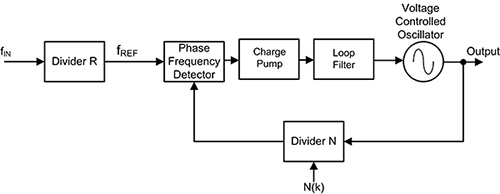

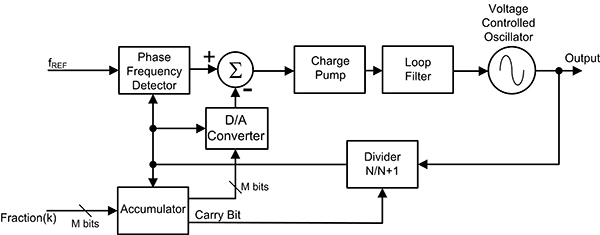

I circuiti PLL sono usati per controllare frequenza e fase. Possono essere configurati come generatori di clock, moltiplicatori di frequenza, demodulatori, generatori di tracciamento o circuiti di recupero del clock. Ognuna di queste applicazioni richiede caratteristiche diverse, ma tutte usano lo stesso concetto di circuito di base. La Figura 1 mostra un diagramma a blocchi di un PLL di base configurato come moltiplicatore di frequenza.

Figura 1: Diagramma a blocchi di un classico sintetizzatore di frequenza a N intero con circuito ad aggancio di fase. (Immagine per gentile concessione di DigiKey)

Figura 1: Diagramma a blocchi di un classico sintetizzatore di frequenza a N intero con circuito ad aggancio di fase. (Immagine per gentile concessione di DigiKey)

Il funzionamento di questo circuito è quello tipico di tutti i circuiti ad aggancio di fase. Fondamentalmente si tratta di un sistema di controllo della retroazione che controlla la fase di un oscillatore controllato in tensione (VCO). Il segnale di ingresso è applicato a un divisore prescaler, che divide la frequenza di ingresso per un fattore R. L'uscita del prescaler è la frequenza di riferimento, che forma un ingresso di un rilevatore a frequenza di fase (PFD).

L'altro ingresso PFD è un segnale di retroazione dal risultato di una divisione per il contatore N. Normalmente, se il PLL è bloccato, le frequenze di entrambi i segnali saranno quasi identiche. L'uscita del rilevatore di fase è una tensione proporzionale alla differenza di fase tra i due ingressi. Se l'anello è sbloccato, come accade all'avvio o in presenza di una grande variazione istantanea nella frequenza di ingresso, il rilevatori di frequenza di fase devia la frequenza operativa PLL verso l'impostazione desiderata. Quando raggiunge questa frequenza, il PFD torna in modalità rilevatore di rilevamento di fase e ha un'uscita proporzionale alla differenza di fase tra la frequenza di riferimento e il segnale di retroazione.

Il rilevatori di frequenza di fase pilota una pompa di carica, che è una fonte di corrente bipolare commutata. Questo significa che può emettere impulsi di corrente positivi e negativi nel filtro ad anello del PLL.

Il filtro ad anello livella il segnale di errore di fase e determina anche le caratteristiche dinamiche del PLL. Il segnale filtrato controlla il VCO. Tenere presente che l'uscita del VCO è a una frequenza pari a N volte l'ingresso fornito all'ingresso di riferimento della frequenza al rilevatore di frequenza di fase ed è pari a N/R moltiplicato per l'ingresso di frequenza. Questo segnale di uscita viene rimandato al rilevatore di fase tramite la divisione per il contatore N.

In genere il filtro ad anello è progettato per corrispondere alle caratteristiche richieste dall'applicazione del PLL. Se il PLL deve acquisire e tracciare un segnale, la larghezza di banda del filtro ad anello sarà maggiore rispetto a quella che si avrebbe se aspettasse una frequenza di ingresso fissa. Il campo di frequenza che il PLL accetterà e sulla quale si attesterà è detto intervallo di acquisizione. Una volta che il PLL è bloccato e insegue un segnale, l'intervallo delle frequenze che seguirà viene detto intervallo di tracciamento. In genere, l'intervallo di tracciamento è maggiore di quello di acquisizione. Il filtro ad anello del PLL determina anche la velocità con cui la frequenza del segnale può cambiare e mantenere comunque l'aggancio, ossia la velocità di variazione massima. Più stretta è la larghezza di banda del filtro ad anello, più piccolo è l'errore di fase ottenibile. Questo a scapito di una risposta più lenta e di un minore intervallo di acquisizione. I PLL utilizzati nelle applicazioni di clock operano principalmente a frequenze fisse. In generale, la larghezza di banda del filtro ad anello dovrebbe essere molto inferiore alla frequenza di riferimento.

Poiché la frequenza di uscita del PLL è un multiplo intero della frequenza di riferimento, la sua risoluzione di frequenza è uguale alla frequenza di riferimento. Ottenere una risoluzione di frequenza più fine richiede la diminuzione della frequenza di riferimento, cosa che fa R dek contatore pre-scaler.

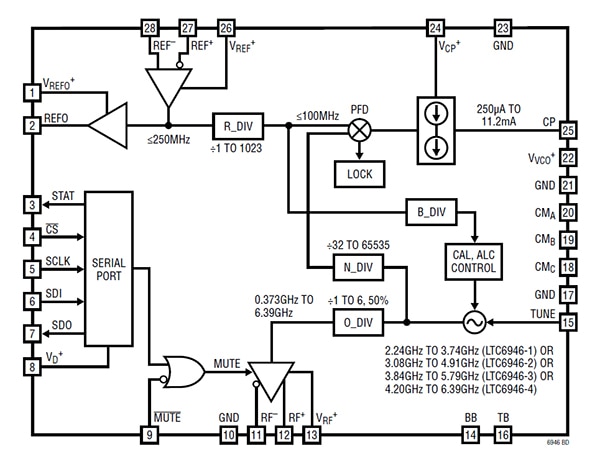

Un esempio commerciale di un sintetizzatore di frequenza a N intero è LTC6946IUFD-3#PBF di Analog Devices, un sintetizzatore a basso rumore da 0,64 a 5,790 GHz con un VCO integrato ed eccellenti prestazioni spurie (Figura 2). Fa parte di una famiglia di quattro sintetizzatori in CI, ciascuno con un campo di frequenza diverso, per un totale da 0,373 a 6,390 GHz.

Figura 2: Diagramma a blocchi del sintetizzatore di frequenza a N intero LTC6946IUFD-3#PBF di Analog Devices con VCO integrato. (Immagine per gentile concessione di Analog Devices)

Figura 2: Diagramma a blocchi del sintetizzatore di frequenza a N intero LTC6946IUFD-3#PBF di Analog Devices con VCO integrato. (Immagine per gentile concessione di Analog Devices)

Questo sintetizzatore richiede un filtro ad anello esterno fornito dall'utente, che può essere ottimizzato per l'applicazione specifica. Esiste un divisore interno del contatore pre-scaler con una intervallo di divisione da 1 a 1023. Il divisore dell'anello ha una intervallo da 32 a 65535. La corrente della pompa di carica è regolabile da 250 µA a 11,2 mA per adattarsi ai requisiti del filtro ad anello.

Sintetizzatori con circuito ad aggancio di fase a N frazionario

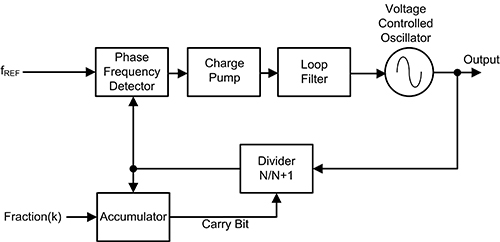

La risoluzione di frequenza del sintetizzatore PLL può essere migliorata riducendo la dimensione del passo a valori inferiori all'intero, cioè con passi frazionari nel divisore dell'anello (N). Questo avviene variando dinamicamente il valore del conto alla rovescia. Ciò significa che l'impostazione del divisore mantiene il valore N per un numero fisso di cicli della frequenza di uscita del PLL e viene scalato periodicamente a un valore diverso, come N+1. Ad esempio, se l'impostazione del divisore è 4 per tre periodi di riferimento e 5 per il quarto ciclo di riferimento, il conto alla rovescia effettivo è 4,25. Un modo per realizzare tutto ciò consiste nell'utilizzare un accumulatore, come mostra la Figura 3.

Figura 3: Diagramma a blocchi di un sintetizzatore PLL a N frazionario che usa un accumulatore per modulare il conteggio del divisore. (Immagine per gentile concessione di DigiKey)

Figura 3: Diagramma a blocchi di un sintetizzatore PLL a N frazionario che usa un accumulatore per modulare il conteggio del divisore. (Immagine per gentile concessione di DigiKey)

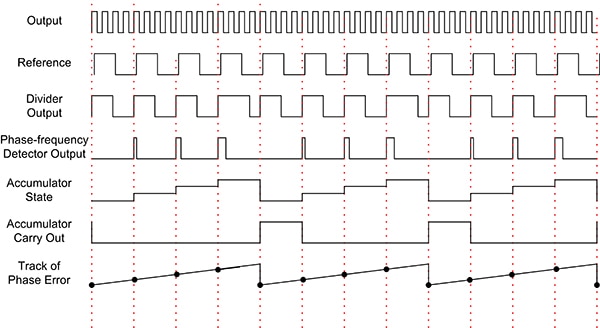

L'accumulatore conta gli impulsi in uscita dal divisore e ad ogni M, dove M è il modulo dell'accumulatore, emette un bit di riporto che cambia l'ingresso del divisore. La Figura 4 continua l'esempio di un divisore frazionario con l'impostazione di 4,25.

Figura 4: Schema di temporizzazione di un sintetizzatore a N frazionario che usa un accumulatore. (Immagine per gentile concessione di DigiKey)

Figura 4: Schema di temporizzazione di un sintetizzatore a N frazionario che usa un accumulatore. (Immagine per gentile concessione di DigiKey)

L'accumulatore è pilotato dall'uscita divisa e conta modulo quattro, cioè M è uguale a quattro. Ogni quarto impulso genera un'uscita di riporto, che aumenta di uno il conteggio del divisore. L'accumulatore si reimposta e ricomincia a contare. L'aumento dell'impostazione del divisore sposta la frequenza di uscita, il che si traduce in un errore di offset di fase accumulato. La traccia dell'errore di fase mostra il valore dell'impulso in funzione del tempo.

L'impostazione media del divisore è 4,25, ma l'uscita del sintetizzatore è modulata in fase, con conseguenti toni spuri nell'uscita. Guardando lo stato dell'accumulatore è ovvio che segue l'errore di fase. Questo può essere usato per rimuovere la modulazione come mostra lla Figura 5.

Figura 5: Utilizzo dello stato dell'accumulatore convertito D/A per annullare la modulazione di fase dovuta alla variazione dinamica N frazionario. (Immagine per gentile concessione di DigiKey)

Figura 5: Utilizzo dello stato dell'accumulatore convertito D/A per annullare la modulazione di fase dovuta alla variazione dinamica N frazionario. (Immagine per gentile concessione di DigiKey)

Lo stato dell'accumulatore è convertito in analogico da un convertitore digitale/analogico (D/A) e scalato e sottratto dall'uscita del rilevatore di frequenza di fase per annullare la modulazione di fase dovuta alla variazione dinamica N frazionario. È necessario prestare molta attenzione: se il segnale di correzione non corrisponde precisamente all'errore di fase, risulteranno toni spuri all'uscita.

Ecco il modulatore sigma-delta

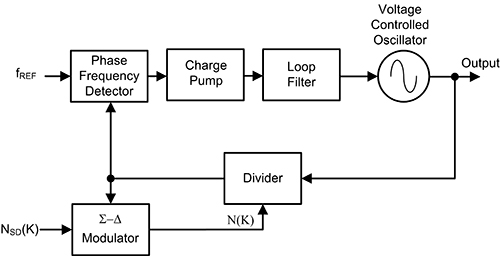

La periodicità nell'accumulatore è la causa delle uscite spurie del sintetizzatore. Sostituendo l'accumulatore con un modulatore sigma-delta, si possono applicare tecniche digitali per modulare il conteggio del divisore in modo da ridurre al minimo le risposte spurie e il rumore. Questa sostituzione è illustrata nella Figura 6.

Figura 6: La sostituzione dell'accumulatore con un modulatore sigma-delta permette di applicare tecniche digitali per variare il conteggio del divisore al fine di ridurre al minimo le risposte spurie. (Immagine per gentile concessione di DigiKey)

Figura 6: La sostituzione dell'accumulatore con un modulatore sigma-delta permette di applicare tecniche digitali per variare il conteggio del divisore al fine di ridurre al minimo le risposte spurie. (Immagine per gentile concessione di DigiKey)

Esistono due tecniche digitali comuni impiegate nella topologia di modulazione sigma-delta. La prima consiste nell'aumentare il numero di conteggi del divisore N su un intervallo di valori più ampio, in modo che il fattore di divisione medio produca il valore del divisore frazionario desiderato. Questo ridurrà i segnali spuri frazionari primari. Il sintetizzatore basato sull'accumulatore varia il conteggio tra due stati. Questo è un metodo di modulazione del primo ordine. Un PLL frazionario sigma-delta di ennesimo ordine modula il contatore N tra 2n valori diversi. Ad esempio, un modulatore del terzo ordine alternerebbe tra otto diversi valori del divisore e un modulatore del quarto ordine alternerebbe tra 16 diversi valori del divisore.

La seconda tecnica digitale, detta anche sottoquantizzazione con rumore casuale o variazione dinamica, consiste nel randomizzare la sequenza 2N in modo che sia pseudocasuale. Pur mantenendo un rapporto di divisione frazionario medio, converte i segnali spuri frazionari in rumore casuale sagomato in modo tale che possa essere filtrato dal PLL.

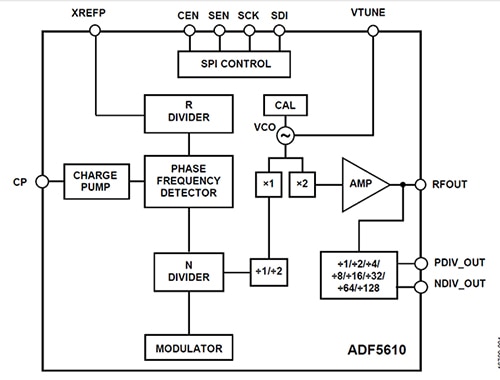

Una versione commerciale di un sintetizzatore sigma-delta a N frazionario è ADF5610BCCZ di Analog Devices, un sintetizzatore a basso rumore da 0,57 MHz a 14,6 GHz con un VCO integrato (Figura 7).

Figura 7: Diagramma a blocchi di ADF5610BCCZ di Analog Devices che supporta entrambe le configurazioni di sintetizzatore a N intero o frazionario. (Immagine per gentile concessione di Analog Devices)

Figura 7: Diagramma a blocchi di ADF5610BCCZ di Analog Devices che supporta entrambe le configurazioni di sintetizzatore a N intero o frazionario. (Immagine per gentile concessione di Analog Devices)

ADF5610 richiede un oscillatore di riferimento esterno e un filtro ad anello. Ha un VCO integrato con una frequenza fondamentale da 3650 a 7300 MHz. Queste frequenze sono raddoppiate internamente e indirizzate al pin RFOUT. Vi è una uscita differenziale che permette alla frequenza VCO raddoppiata di essere divisa per fattori di 1, 2, 4, 8, 16, 32, 64, o 128, per generare frequenze di uscita RF fino a 57 MHz.

ADF5610 utilizza un modulatore sigma-delta avanzato con un modulo frazionario a 24 bit che raggiunge livelli spuri eccezionalmente bassi. Come per tutti i sintetizzatori che utilizzano un modulatore sigma-delta, questo dispositivo utilizza tecniche di elaborazione di segnali digitali per trovare il rapporto frazionario medio desiderato. Questo processo, sincronizzato alla velocità PFD, produce un rumore di modulazione in uscita detto rumore di quantizzazione con una risposta in frequenza passa-alto. Il filtro esterno passa-basso è usato per filtrare questo rumore di quantizzazione a un livello inferiore al rumore di fase del VCO, evitando così che il rumore contribuisca al rumore di fase generale del sistema.

ADF5610 include anche una modalità di frequenza esatta per un errore di frequenza di 0 Hz. Questa modalità è in grado di generare frequenze esatte tra i passi N interi adiacenti, pur continuando a utilizzare l'intero modulo dell'accumulatore di fase a 24 bit. Raggiunge passi di frequenza esatti con un alto tasso di confronto del rilevatore di fase, permettendo al PLL di mantenere un eccellente rumore di fase e prestazioni spurie in questa modalità.

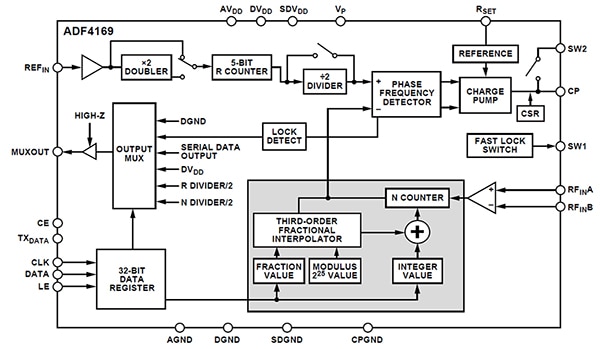

ADF4169CCPZ-RL7 di Analog Devices è un altro sintetizzatore PLL configurabile come un dispositivo a N intero o N frazionario. Funziona con una larghezza di banda RF fino a 13,5 GHz con modulazione e generazione di forme d'onda. Utilizza un ingresso esterno per la frequenza di riferimento, un VCO e un filtro ad anello. Ha un modulatore sigma-delta del terzo ordine per la sintesi N frazionaria che può essere disabilitato, permettendo al dispositivo di funzionare in modalità N intero (Figura 8).

Figura 8: ADF4169CCPZ-RL7 di Analog Devices utilizza un modulatore sigma-delta del terzo ordine. (Immagine per gentile concessione di Analog Devices)

Figura 8: ADF4169CCPZ-RL7 di Analog Devices utilizza un modulatore sigma-delta del terzo ordine. (Immagine per gentile concessione di Analog Devices)

Il sintetizzatore ADF4158WCCPZ-RL7 è destinato all'uso nei radar a onda continua modulata in frequenza (FMCW). Supporta vari tipi di forme d'onda modulate nel dominio della frequenza, comprese le rampe a dente di sega e triangolari. Questa è una caratteristica speciale necessaria nelle applicazioni radar.

Conclusione

L'aumento della velocità dati nei bus di comunicazione seriale ad alta velocità richiede ai progettisti di guardare oltre i sintetizzatori digitali diretti, che funzionano meglio sotto i 3 GHz, per trovare soluzioni di generazione del clock di sistema. I sintetizzatori di frequenza basati su PLL che utilizzano topologie a N intero e N frazionario forniscono segnali stabili e a basso rumore per i clock ad alta frequenza, le comunicazioni dati seriali e le applicazioni radar per frequenze nell'ordine di decine di gigahertz.

Esonero della responsabilità: le opinioni, le convinzioni e i punti di vista espressi dai vari autori e/o dai partecipanti al forum su questo sito Web non riflettono necessariamente le opinioni, le convinzioni e i punti di vista di DigiKey o le sue politiche.