Come utilizzare i SoC FPGA per sistemi in tempo reale sicuri e connessi

Contributo di Editori nordamericani di DigiKey

2023-02-16

Gli FPGA (gate array programmabili sul campo), i sottosistemi di microcontroller (MCU) RISC-V con capacità Linux, le architetture di memoria avanzate e le interfacce di comunicazione ad alte prestazioni sono strumenti importanti per i progettisti. Ciò è particolarmente vero per i progettisti di sistemi connessi sicuri, di sistemi critici per la sicurezza e di un'ampia gamma di sistemi deterministici in tempo reale come l'intelligenza artificiale (IA) e l'apprendimento automatico (ML).

Tuttavia, l'integrazione di questi diversi elementi in un sistema sicuro, connesso e deterministico può essere impegnativa, così come la realizzazione delle interconnessioni ad alta velocità per i vari elementi del sistema. I progettisti devono includere un'unità di gestione della memoria, un'unità di protezione della memoria, una capacità di avvio sicuro e transceiver di classe gigabit per la connettività ad alta velocità. Il progetto richiede la gestione dell'alimentazione attiva e statica e il controllo delle correnti di inserzione. Alcuni progetti richiederanno il funzionamento nell'intervallo di temperatura commerciale esteso da 0 a +100 °C di temperatura di giunzione (TJ), mentre i sistemi in ambienti industriali dovranno funzionare con TJ comprese tra -40 e +100 °C.

Per affrontare queste e altre sfide, i progettisti possono rivolgersi ai dispositivi SoC (System-on-Chip) FPGA, che combinano basso consumo energetico, efficienza termica e sicurezza a livello di difesa per sistemi intelligenti, connessi e deterministici.

Questo articolo esamina l'architettura di un SoC FPGA di questo tipo e come questo supporta la progettazione efficiente di sistemi connessi e deterministici. Presenta quindi il benchmark EEMBC CoreMark-PRO per la potenza di elaborazione e il consumo energetico e una panoramica delle prestazioni benchmark di un SoC FPGA rappresentativo. L'articolo analizza il modo in cui la sicurezza viene integrata in questi SoC FPGA e illustra alcuni SoC FPGA di Microchip Technology, insieme a una piattaforma di sviluppo per accelerare il processo di progettazione. Si conclude con un breve elenco di schede di espansione di MikroElektronika che possono essere utilizzate per implementare una serie di interfacce di comunicazione, nonché la capacità di localizzazione di un sistema di navigazione satellitare globale (GNSS).

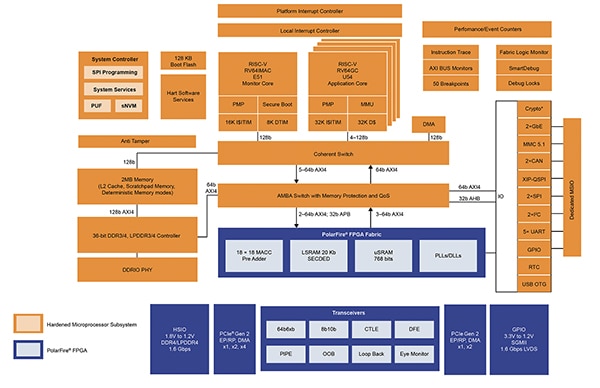

SoC realizzati con un tessuto FPGA

Il 'chip' di questo SoC è un tessuto FPGA che contiene gli elementi del sistema, dall'FPGA al sottosistema MCU RISC-V, realizzato con logica FPGA protetta. Il sottosistema MCU comprende un cluster MCU RISC-V quad core, un core di monitoraggio RISC-V, un controller di sistema e un sottosistema di memoria di livello 2 (L2) deterministico. L'FPGA di questi SoC comprende fino a 460.000 elementi logici, transceiver fino a 12,7 Gbps e altri blocchi di ingresso/uscita (I/O), tra cui I/O generale (GPIO) e Peripheral Component Interconnect express (PCIe) 2. L'architettura complessiva è progettata nell'ottica dell'affidabilità. Include la correzione di un singolo errore e il rilevamento di un doppio errore (SECDED) su tutte le memorie, l'analisi della potenza differenziale (DPA), la protezione della memoria fisica e 128 kbit di memoria flash di avvio (Figura 1).

Figura 1: Tutti gli elementi di questo SoC FPGA, compresi i sottosistemi RISC-V, sono implementati sul tessuto FPGA. (Immagine per gentile concessione di Microchip Technology)

Figura 1: Tutti gli elementi di questo SoC FPGA, compresi i sottosistemi RISC-V, sono implementati sul tessuto FPGA. (Immagine per gentile concessione di Microchip Technology)

Microchip offre l'ecosistema Mi-V di strumenti di produttori terzi e risorse di progettazione per supportare l'implementazione dei sistemi RISC-V. È stato realizzato per accelerare l'adozione dell'architettura del set di istruzioni (ISA) RISC-V per hard core RISC-V e per soft core RISC-V. Gli elementi dell'ecosistema Mi-V includono l'accesso a:

- Licenze di proprietà intellettuale (IP)

- Hardware

- Sistemi operativi e middleware

- Debugger, compilatori e servizi di progettazione

Gli MCU RISC-V hard nel SoC FPGA includono diverse funzionalità di debug, come l'interfaccia estensibile avanzata (AXI) configurabile in runtime passivo e la traccia delle istruzioni. AXI consente ai progettisti di monitorare i dati scritti o letti da varie memorie e di sapere quando sono scritti o letti.

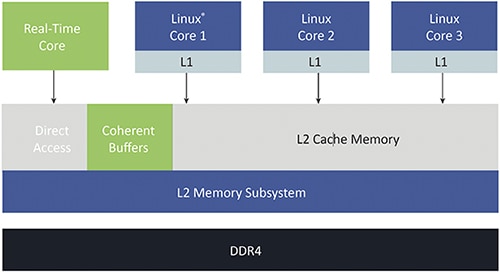

Il sottosistema MCU RISC-V utilizza una pipeline in-order a cinque stadi e a singolo ordine. Non è vulnerabile agli attacchi Spectre o Meltdown che possono affliggere le architetture non ordinate. Tutti e cinque gli MCU sono coerenti con il sottosistema di memoria e supportano un mix di sistemi in tempo reale deterministici in modalità multi-processing asimmetrico (AMP) e Linux. Le capacità del sottosistema RISC-V includono (Figura 2):

- Eseguire operazioni hard in tempo reale con Linux

- Configurare L1 e L2 come memoria deterministica

- Sottosistema di memoria DDR4

- Disabilitare/abilitare i predittori di ramo

- Funzionamento della pipeline in-order

Figura 2: Il sottosistema RISC-V comprende diversi elementi di processore e di memoria. (Immagine per gentile concessione di Microchip Technology)

Figura 2: Il sottosistema RISC-V comprende diversi elementi di processore e di memoria. (Immagine per gentile concessione di Microchip Technology)

Più elaborazione con meno energia

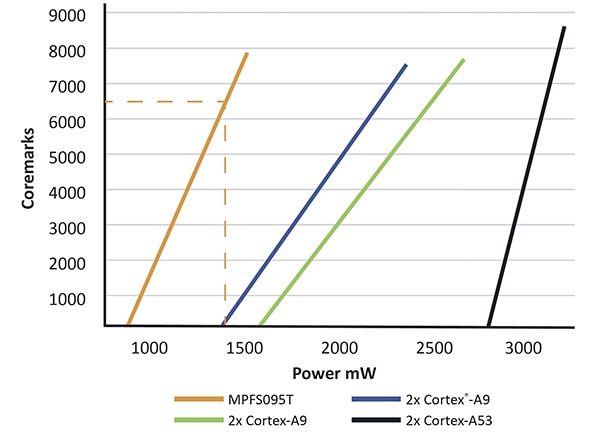

Oltre ai vantaggi del funzionamento del sistema, tra cui il supporto per l'elaborazione in tempo reale, questi SoC FPGA sono ad alta efficienza energetica. Il benchmark EEMBC CoreMark-PRO è uno standard del settore che confronta l'efficienza e le prestazioni degli MCU nei sistemi embedded. È stato concepito appositamente per il benchmark delle prestazioni hardware e per sostituire il benchmark Dhrystone.

I carichi di lavoro CoreMark-PRO comprendono una varietà di caratteristiche prestazionali, parallelismo a livello di istruzioni e utilizzo della memoria, basati su quattro carichi di lavoro in virgola mobile e cinque carichi di lavoro integrali comuni. I carichi di lavoro in virgola mobile comprendono una routine algebrica lineare derivata da LINPACK, una trasformata di Fourier veloce, un algoritmo di rete neurale per la valutazione dei modelli e una versione migliorata del benchmark Livermore. La compressione JPEG, un parser XML, la compressione ZIP e un algoritmo hash sicuro a 256 bit (SHA-256) costituiscono la base dei carichi di lavoro integrali.

I modelli MPFSO95T di questi SoC FPGA, come MPFS095TL-FCSG536E, possono fornire fino a 6.500 Coremark a 1,3 W (Figura 3).

Figura 3: Il SoC FPGA MPFS095T (linea arancione) fornisce 6500 Coremark a 1,3 W. (Immagine per gentile concessione di Microchip Technology)

Figura 3: Il SoC FPGA MPFS095T (linea arancione) fornisce 6500 Coremark a 1,3 W. (Immagine per gentile concessione di Microchip Technology)

Considerazioni sulla sicurezza

Le applicazioni critiche per la sicurezza e in tempo reale di questi SoC FPGA richiedono un alto livello di sicurezza, oltre a un'elevata efficienza energetica e a potenti capacità elaborative. Le funzioni di sicurezza di base di questi SoC FPGA comprendono la programmazione bitstream resistente all'analisi di potenza differenziale (DPA), un vero generatore di numeri casuali (TRNG) e una funzione fisicamente non clonabile (PUF). Includono inoltre l'avvio sicuro standard e definito dall'utente, la protezione della memoria fisica che fornisce restrizioni di accesso alla memoria in relazione allo stato di privilegio della macchina, comprese le modalità macchina, supervisore o utente e l'immunità dagli attacchi Meltdown e Spectre.

La sicurezza inizia con una gestione sicura della supply chain, compreso l'uso di moduli di sicurezza hardware (HSM) durante il test e il confezionamento dei wafer. L'uso di un certificato FPGA a firma digitale x.509 a 768 byte incorporato in ogni SoC FPGA aggiunge sicurezza alla supply chain.

Questi SoC FPGA includono numerosi rilevatori di manomissione su chip per garantire un funzionamento sicuro e affidabile. Se viene rilevata una manomissione, un flag di manomissione consente al sistema di reagire come necessario. Alcuni dei rilevatori di manomissione disponibili includono:

- Monitor di tensione

- Sensori di temperatura

- Rilevatori di glitch del clock e della frequenza di clock

- Rilevatore attivo JTAG

- Rilevatore attivo di rete a maglie

La sicurezza è ulteriormente garantita da contromisure di cifratura simmetrica a blocchi a 256 bit con standard di crittografia avanzata (AES-256), da funzionalità di digest crittografico integrato per garantire l'integrità dei dati, da PUF integrato per la memorizzazione delle chiavi e da funzionalità di azzeramento per il tessuto FPGA e per tutte le memorie su chip.

Esempi di SoC FPGA

Microchip Technology combina queste capacità e tecnologie nei suoi SoC FPGA PolarFire con diversi gradi di velocità, temperature nominali e contenitori di varie dimensioni per supportare le esigenze dei progettisti in un'ampia gamma di soluzioni con elementi logici compresi tra 25.000 e 460.000. Sono disponibili quattro gradi di temperatura (tutti classificati per TJ), un intervallo commerciale esteso da 0 a +100 °C, un intervallo industriale da -40 a +100 °C, un intervallo automotive da -40 a +125 °C e un intervallo militare da -55 a +125 °C.

I progettisti possono scegliere tra dispositivi a velocità standard o dispositivi a velocità -1, più veloci del 15%. Questi SoC FPGA possono funzionare a 1,0 V per il funzionamento a basso consumo o a 1,05 V per prestazioni più elevate. Sono disponibili in un'ampia gamma di dimensioni, tra cui 11 x 11 mm, 16 x 16 mm e 19 x 19 mm.

Per le applicazioni che richiedono un funzionamento a temperature commerciali estese, un funzionamento a velocità standard e 24.000 elementi logici in un contenitore di 19 x 19 mm, i progettisti possono utilizzare il modello MPFS250T-FCVG484EES. Per soluzioni più semplici che richiedono 23.000 elementi logici, i progettisti possono rivolgersi al modello MPFS025T-FCVG484E, anch'esso con funzionamento a temperature commerciali estese e velocità standard in un contenitore di 19 x 19 mm. MPFS250T-1FCSG536T2 con 254.000 elementi logici è destinato a sistemi automotive ad alte prestazioni e offre un intervallo della temperatura di funzionamento compreso tra -40 e 125 °C e un grado di velocità -1 per un clock del 15% più veloce, in un contenitore compatto di 16 x 16 mm a 536 sfere su un passo di 0,5 mm (Figura 4).

Figura 4: MPFS250T-1FCSG536T2 per il settore automotive è disponibile in un contenitore di 16 x 16 mm a 536 sfere su un passo di 0,5 mm. (Immagine per gentile concessione di Microchip Technology)

Figura 4: MPFS250T-1FCSG536T2 per il settore automotive è disponibile in un contenitore di 16 x 16 mm a 536 sfere su un passo di 0,5 mm. (Immagine per gentile concessione di Microchip Technology)

Piattaforma di sviluppo SoC FPGA

Per accelerare la progettazione dei sistemi con il SoC FPGA PolarFire, Microchip offre il kit MPFS-ICICLE-KIT-ES PolarFire SoC Icicle con cui esplorare il sottosistema di microprocessori RISC-V a cinque core con capacità Linux ed esecuzione in tempo reale a basso consumo. Il kit comprende una licenza gratuita per Libero Silver, necessaria per valutare i progetti. Supporta funzioni di programmazione e debug in un unico linguaggio.

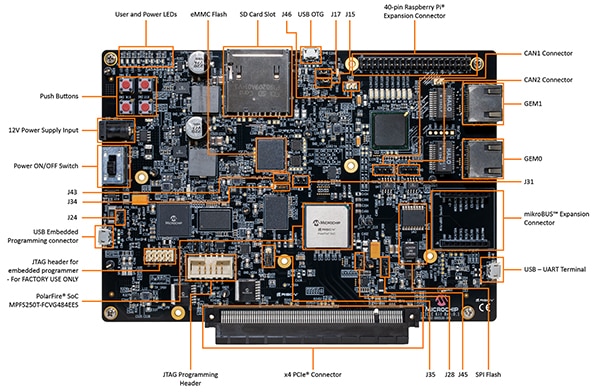

Questi SoC FPGA sono supportati dal kit di sviluppo software (SDK) dell'acceleratore VectorBlox, che consente di realizzare applicazioni IA/ML a basso consumo in fattore di forma compatto. L'accento è posto sulla semplificazione della progettazione, al punto che non è necessario che i progettisti abbiano una precedente esperienza di progettazione di FPGA. L'SDK dell'acceleratore VectorBlox consente agli sviluppatori di programmare reti neurali ad alta efficienza energetica in linguaggio C/C++. Il kit Icicle è dotato di numerose funzioni per fornire un ambiente di sviluppo completo, tra cui un sistema di sensori di potenza multi-rail per monitorare i vari domini di potenza, una porta radice PCIe e memorie su scheda, tra cui LPDDR4, QSPI e eMMC Flash per l'esecuzione di Linux e Raspberry Pi, nonché porte di espansione mikroBUS per una serie di opzioni di connettività cablata e wireless, oltre a estensioni funzionali come la capacità di localizzazione GNSS (Figura 5).

Figura 5: Questo ambiente di sviluppo del SoC FPGA completo include i connettori per le schede di espansione Raspberry Pi (in alto a destra) e mikroBUS (in basso a destra). (Immagine per gentile concessione di Microchip Technology)

Figura 5: Questo ambiente di sviluppo del SoC FPGA completo include i connettori per le schede di espansione Raspberry Pi (in alto a destra) e mikroBUS (in basso a destra). (Immagine per gentile concessione di Microchip Technology)

Schede di espansione

Alcuni esempi di schede di espansione mikroBUS includono:

MIKROE-986, per aggiungere la connettività bus CAN utilizzando un'interfaccia periferica seriale (SPI).

MIKROE-1582, per l'interfacciamento tra l'MCU e un bus RS-232.

MIKROE-989, per il collegamento con un bus di comunicazione RS422/485.

MIKROE-3144 supporta le tecnologie LTE Cat M1 e NB1, per una connettività affidabile e semplice con i dispositivi IoT 3GPP.

MIKROE-2670 abilita la funzionalità GNSS con la ricezione simultanea delle costellazioni GPS e Galileo e di BeiDou o GLONASS, garantendo un'elevata precisione posizionale in caso di segnali deboli o di interferenze nelle aree urbane.

Conclusione

I progettisti possono rivolgersi ai SoC FPGA per sviluppare sistemi deterministici connessi, critici per la sicurezza e in tempo reale. I SoC FPGA forniscono un'ampia gamma di elementi di sistema, tra cui un tessuto FPGA, un sottosistema MCU RISC-V con memorie ad alte prestazioni, interfacce di comunicazione ad alta velocità e numerose funzioni di sicurezza. Per aiutare i progettisti, sono disponibili schede di sviluppo e ambienti completi di tutti gli elementi necessari, comprese le schede di espansione necessarie per implementare un'ampia gamma di comunicazioni e funzioni di localizzazione.

Letture consigliate

Esonero della responsabilità: le opinioni, le convinzioni e i punti di vista espressi dai vari autori e/o dai partecipanti al forum su questo sito Web non riflettono necessariamente le opinioni, le convinzioni e i punti di vista di DigiKey o le sue politiche.