Come valutare e utilizzare buffer di clock a ritardo zero per proteggere la temporizzazione nei sistemi digitali sincroni

Contributo di Editori nordamericani di DigiKey

2019-07-18

Con l'aumentare delle prestazioni dei sistemi digitali, i progettisti devono prestare sempre più attenzione alla progettazione dei circuiti di generazione e distribuzione dei segnali di clock per evitare differenze o incertezze nella temporizzazione di questa distribuzione. Questo tipo di problemi può deteriorare le prestazioni del sistema, ridurre i margini di temporizzazione o causare errori funzionali. Per evitare problemi legati allo skew della temporizzazione, possono utilizzare buffer di clock a ritardo zero.

I tipici sistemi digitali sincroni utilizzano un clock comune per mantenere le operazioni in sequenza. Per mantenere il sistema operativo alla velocità desiderata, questo clock deve essere distribuito a tutti gli elementi sequenziali, spesso utilizzando il controllo ad anello chiuso per ridurre lo skew di temporizzazione. I buffer di clock a ritardo zero utilizzano anelli con blocco di fase (PLL) per garantire che le uscite bufferizzate del clock siano allineate con l'ingresso del clock di riferimento, assicurando una temporizzazione quasi perfetta.

Questo articolo descriverà i buffer di clock a ritardo zero, spiegherà come funzionano usando le soluzioni di esempio di Cypress Semiconductor, Integrated Device Technology Inc. (IDT) e ON Semiconductor e illustrerà nei dettagli come controllare lo skew del clock. Si occuperà inoltre dei metodi di prova per garantire la stabilità di questi dispositivi.

Skew del clock

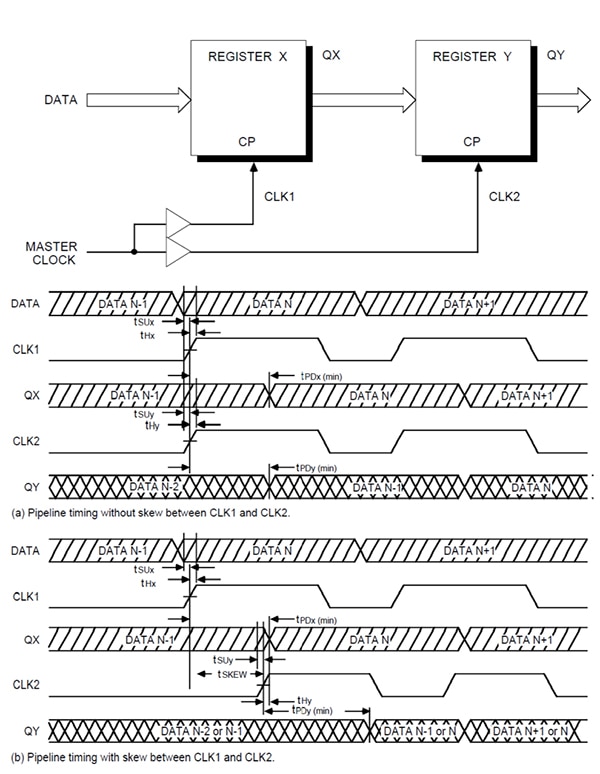

Nei sistemi digitali sincroni, i segnali di clock possono arrivare in momenti diversi alle varie parti del circuito, causando il cosiddetto skew del clock. Lo skew del clock può ridurre i margini di temporizzazione e provocare il guasto del sistema (Figura 1).

Figura 1: Un semplice esempio di come lo skew del clock possa incidere sulle operazioni di un registro della pipeline. Un clock con skew può violare i requisiti di installazione e/o mantenimento, portando a uno stato di uscita indeterminato. (Immagine per gentile concessione di IDT)

Figura 1: Un semplice esempio di come lo skew del clock possa incidere sulle operazioni di un registro della pipeline. Un clock con skew può violare i requisiti di installazione e/o mantenimento, portando a uno stato di uscita indeterminato. (Immagine per gentile concessione di IDT)

Prendiamo in considerazione un semplice sistema sincrono composto da due registri. I dati vengono messi nella pipeline tramite i registri in modo che QX, l'uscita del registro X, sia l'ingresso al registro Y. I clock vengono inviati ai registri tramite buffer indipendenti chiamati CLK1 e CLK2. Se tra i clock non c'è nessuno skew, come mostrato nello schema (a), lo stato dei dati N, che soddisfa i requisiti del tempo di impostazione del registro (tSUx) e di mantenimento (tHx), viene sincronizzato con QX, l'uscita del registro X, sul primo margine di clock dopo il ritardo di propagazione del registro. Lo stesso margine di clock su CLK2 fa sì che lo stato precedente di QX, N-1, venga letto dal registro e appaia all'uscita QY dopo il ritardo di propagazione del registro.

Se è presente uno skew di tempo tra CLK1 e CLK2, come mostrato nello schema (b), lo stato di QX potrebbe essere in transizione quando si verifica CLK2. L'ingresso al registro Y potrebbe non soddisfare i requisiti di impostazione del registro o di tempo di mantenimento e l'uscita potrebbe essere indeterminata e provocare di conseguenza un errore.

Per assicurare uno skew del clock minimo, i progettisti abbinano le lunghezze delle tracce dei circuiti stampati, selezionano buffer e altri componenti di clock con ritardi di propagazione simili e bilanciano il carico sulle varie sorgenti di clock. Anche se queste tecniche aiutano, per ottenere un buon controllo dello skew del clock in genere è richiesto l'uso di buffer di clock a ritardo zero.

Controllo dello skew del clock

Lo skew del clock può derivare da molte sorgenti. La più ovvia sono i segnali di clock instradati su interconnessioni di varie lunghezze del circuito stampato. Vi sono poi i casi dei clock che passano per diversi dispositivi attivi con diversi ritardi di propagazione, dei buffer di clock con carichi diversi, o differenze di temperatura nei buffer. Anche se alcuni di questi effetti possono essere controllati, spesso i progettisti usano dispositivi attivi per risincronizzare i clock su un clock di riferimento utilizzando i PLL.

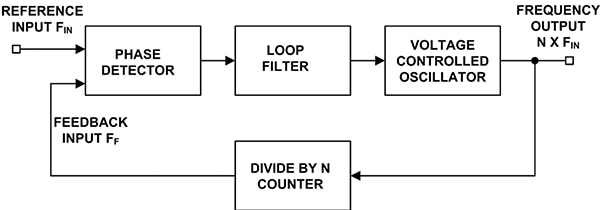

I circuiti PLL sono usati per controllare frequenza e fase. Possono essere configurati come moltiplicatori di frequenza, demodulatori, generatori di tracking o circuiti di recupero del clock. Ognuna di queste applicazioni richiede caratteristiche diverse, ma tutte usano lo stesso concetto di circuito di base mostrato nella Figura 2.

Figura 2: Diagramma a blocchi di un PLL configurato come moltiplicatore di frequenza. Fondamentalmente si tratta di un sistema di controllo della retroazione che controlla la fase di un oscillatore controllato in tensione (VCO). (Immagine per gentile concessione di DigiKey)

Figura 2: Diagramma a blocchi di un PLL configurato come moltiplicatore di frequenza. Fondamentalmente si tratta di un sistema di controllo della retroazione che controlla la fase di un oscillatore controllato in tensione (VCO). (Immagine per gentile concessione di DigiKey)

La Figura 2 mostra un diagramma a blocchi di un PLL di base configurato come moltiplicatore di frequenza. Il funzionamento di questo circuito è quello tipico di tutti i PLL. Fondamentalmente si tratta di un sistema di controllo della retroazione che controlla la fase di un VCO. Il segnale di ingresso viene applicato a un ingresso del rilevatore di fase. L'altro ingresso è un segnale di retroazione dal risultato di una divisione per il contatore N. Normalmente le frequenze di entrambi i segnali saranno quasi identiche.

L'uscita del rilevatore di fase è una tensione proporzionale alla differenza di fase tra i due ingressi. Questo segnale viene applicato al filtro ad anello. È il filtro ad anello che determina le caratteristiche dinamiche del PLL. Il segnale filtrato controlla il VCO. Tenere presente che l'uscita del VCO è a una frequenza pari a N volte l'ingresso fornito all'ingresso di riferimento della frequenza (FIN). Questo segnale di uscita viene rimandato al rilevatore di fase tramite la divisione per il contatore N.

In genere il filtro ad anello è progettato per corrispondere alle caratteristiche richieste dall'applicazione del PLL. Se il PLL deve acquisire e tracciare un segnale, la larghezza di banda del filtro ad anello sarà maggiore rispetto a quella che si avrebbe se aspettasse una frequenza di ingresso fissa. Il campo di frequenza che il PLL accetterà e sulla quale si attesterà è detto intervallo di acquisizione. Una volta che il PLL è bloccato e insegue un segnale, l'intervallo delle frequenze che seguirà viene detto intervallo di tracciamento. In genere, l'intervallo di tracciamento è maggiore di quello di acquisizione. Il filtro ad anello del PLL determina anche la velocità con cui la frequenza del segnale può cambiare e mantenere comunque l'aggancio. Questa è la velocità di variazione massima. Più stretta è la larghezza di banda del filtro ad anello, più piccolo è l'errore di fase ottenibile. Questo a scapito di una risposta più lenta e di un minore intervallo di acquisizione. I PLL utilizzati nelle applicazioni di clock operano principalmente a frequenze fisse.

Buffer di clock a ritardo zero

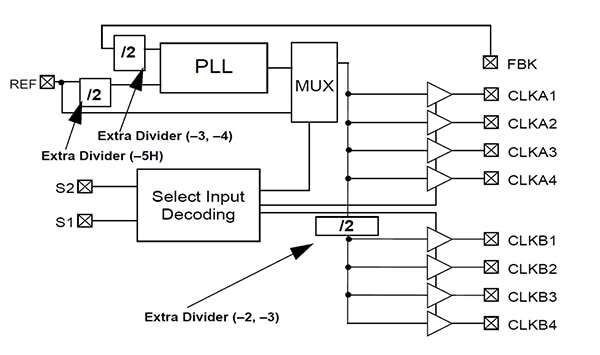

Un buffer a ritardo zero è un dispositivo in grado di bufferizzare un segnale di clock, producendo più uscite di clock da un singolo ingresso del clock di riferimento. Le varie uscite di clock bufferizzate hanno un ritardo minimo o nullo rispetto all'ingresso del clock di riferimento e un basso skew tra le uscite. Nella Figura 3 è riportato il diagramma a blocchi semplificato di un buffer a ritardo zero CY2308SXC-3T di Cypress Semiconductor.

Figura 3: Il buffer a ritardo zero a otto uscite CY2308SXC-3T usa un PLL per sincronizzare tutte le uscite con uno skew del tempo prossimo allo zero. (Immagine per gentile concessione di Cypress Semiconductor)

Figura 3: Il buffer a ritardo zero a otto uscite CY2308SXC-3T usa un PLL per sincronizzare tutte le uscite con uno skew del tempo prossimo allo zero. (Immagine per gentile concessione di Cypress Semiconductor)

Un buffer a ritardo zero è costruito con un PLL integrato che, come ingressi per il suo rilevatore di fase, accetta un ingresso di riferimento (REF) e uno di retroazione (FBK). L'ingresso di retroazione è pilotato da una delle uscite scelte dall'utente. Il rilevatore di fase interno del PLL regola la fase di uscita del VCO in modo che i suoi due ingressi non presentino differenze di fase o di frequenza. Una delle uscite di clock bufferizzate e il suo carico vengono scelti per essere la retroazione al PLL tramite il rilevatore di fase. A prescindere dai cambiamenti del carico su quell'uscita, il PLL li compenserà dinamicamente. Si avrà così un ritardo zero dall'ingresso all'uscita che pilota la retroazione, indipendentemente dal suo carico in uscita.

La famiglia CY2308 ha due banchi di quattro uscite, che operano su un campo di frequenza da 10 a 133 MHz. Lo skew del tempo tra l'ingresso e l'uscita è inferiore a 250 ps e lo skew del clock tra le uscite è inferiore a 200 ps. Lo skew del tempo tra l'ingresso e l'uscita può essere regolato cambiando la capacità di carico sull'uscita utilizzata per l'ingresso di retroazione.

La famiglia di prodotti offre diverse configurazioni di divisori per due. Il componente selezionato è la variante "-3" con due di questi divisori, come mostrato nel diagramma a blocchi. Questa configurazione consente all'utente di ottenere uscite pari a due o quattro volte la frequenza di ingresso del clock di riferimento.

Il buffer a ritardo zero più usato è configurato con cinque uscite e viene offerto da diversi produttori. CY2305SXI-1HT di Cypress Semiconductor, 2305-1DCGI8 di IDT e NB2305AI1HDR2G di ON Semiconductor sono dispositivi molto simili. Presentano tutti cinque uscite di clock bufferizzate, un'unica porta CLKOUT e un banco di uscite di clock quadruplo. Diversamente da CY2308, il punto di retroazione del PLL è fisso sul singolo segnale CLKOUT.

Dinamica del buffer a ritardo zero

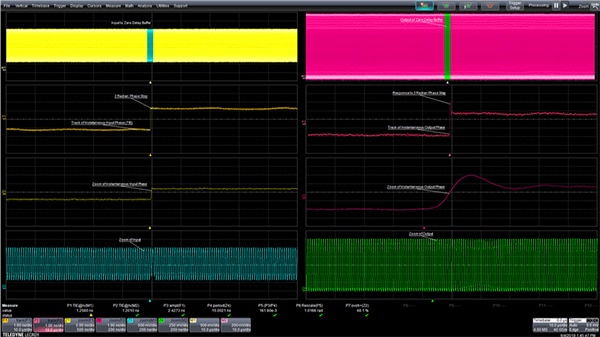

I PLL dei buffer a ritardo zero sono sostanzialmente dei sistemi di controllo della retroazione. La dinamica è controllata dal filtro ad anello del PLL. Come con qualsiasi sistema di controllo, è importante valutare la dinamica dell'anello di retroazione in risposta a un ingresso transitorio. Un modo per farlo è applicare un ingresso con un cambio di gradino per valutarne la risposta (Figura 4).

Figura 4: Valutazione della risposta al gradino da parte del buffer a ritardo zero CY2305 utilizzando un gradino di fase di 1 radiante a 66,67 MHz. La griglia in alto a sinistra è il segnale di ingresso e quella in alto a destra è l'uscita. (Immagine per gentile concessione di DigiKey)

Figura 4: Valutazione della risposta al gradino da parte del buffer a ritardo zero CY2305 utilizzando un gradino di fase di 1 radiante a 66,67 MHz. La griglia in alto a sinistra è il segnale di ingresso e quella in alto a destra è l'uscita. (Immagine per gentile concessione di DigiKey)

Il segnale di ingresso è un seno di 66,67 MHz con gradino di un radiante al centro della finestra del segnale acquisito. Questa forma d'onda è stata generata da un generatore di forme d'onda arbitrarie (AWG). Sia l'ingresso che l'uscita del buffer a ritardo zero CY2305 sono stati acquisiti usando un oscilloscopio con un'impostazione della base del tempo di 10 µs per divisione.

La griglia in alto a sinistra nella Figura 4 è il segnale di ingresso e quella in alto a destra è l'uscita. L'errore dell'intervallo di tempo (TIE) è la differenza di tempo del margine di clock misurato rispetto alla sua posizione ideale e viene misurato per ogni forma d'onda. In sostanza, è la fase istantanea del segnale riferito a una frequenza di clock fissa, in questo caso 66,67 MHz. Il valore del TIE per ogni ciclo di clock, sia dell'ingresso che dell'uscita, viene tracciato come una forma d'onda detta traccia del TIE. La traccia per l'ingresso è la seconda griglia dall'alto a sinistra. Qui il gradino nella fase è visibile con un'ampiezza di 2,4 ns. Questo valore rappresenta una variazione di fase di un radiante per la frequenza di clock di 66,67 MHz.

La seconda traccia dall'alto a destra è quella di uscita del TIE. La traccia dell'uscita mostra una certa sovraelongazione e si assesta su un nuovo valore medio per rispondere al cambio di ingresso. La terza traccia dall'alto è una traccia ingrandita orizzontalmente dell'ingresso a sinistra e dell'uscita a destra. I dettagli del gradino dell'ingresso mostrano una transizione pulita.

L'ingrandimento dell'uscita presenta una certa sovraelongazione, dopo di che si assesta rapidamente sul nuovo valore medio in circa un ciclo della durata di circa 500 ns. Visto il gradino di fase molto ampio, questa è una risposta corretta al gradino. Si assesta rapidamente e non risulta una risposta oscillatoria instabile.

Le due tracce in basso mostrano le viste espanse orizzontalmente dell'ingresso (a sinistra) e dell'uscita (a destra). Il grande gradino di fase è visibile chiaramente nell'ingresso, mentre in questa scala temporale la risposta di uscita lenta lo è meno.

Conclusione

I progettisti di sistemi digitali ad alte prestazioni devono prestare molta attenzione alla progettazione dei circuiti di generazione e distribuzione dei segnali di clock per evitare differenze o incertezze nella temporizzazione di questa distribuzione. Questo tipo di problemi può deteriorare le prestazioni del sistema, ridurre i margini di temporizzazione o causare errori funzionali.

Come descritto, il buffer a ritardo zero è uno strumento valido per il controllo attivo quando si propagano più segnali di clock e si deve mantenere la sincronizzazione con un segnale master. Offre un tracciamento eccellente anche in presenza di variazioni significative del carico sull'uscita rilevata. Tuttavia, come è stato dimostrato, i progettisti devono valutare attentamente la dinamica del circuito di retroazione di un buffer a ritardo zero per assicurarsi che soddisfi i requisiti dell'applicazione.

Esonero della responsabilità: le opinioni, le convinzioni e i punti di vista espressi dai vari autori e/o dai partecipanti al forum su questo sito Web non riflettono necessariamente le opinioni, le convinzioni e i punti di vista di DigiKey o le sue politiche.