Nozioni di base sugli FPGA: cosa sono gli FPGA e perché sono necessari?

Contributo di Editori nordamericani di DigiKey

2019-11-14

Spesso le migliori soluzioni di progettazione sono date da combinazioni di processori RISC, CISC, grafici e FPGA, da soli FPGA o da FPGA dotati di hard core di processore integrati. Tuttavia, molti progettisti non conoscono le capacità degli FPGA, come si sono evoluti e come utilizzarli. Questo articolo, Parte 1 di una serie in cinque parti, illustrerà i fondamenti degli FPGA e presenterà soluzioni di esempio di alcuni dei principali fornitori. Nella Parte 2, Parte 3, Parte 4 e Parte 5 ci concentreremo sulle famiglie di dispositivi FPGA e sugli strumenti di progettazione offerti da Lattice Semiconductor, Microchip, Altera e Xilinx.

I progettisti sono sempre alla ricerca di modi per progettare sistemi che forniscano una soluzione informatica ottimale capace di soddisfare tutti i loro requisiti applicativi. In molte situazioni, questa soluzione ottimale richiede spesso l'uso di gate array programmabili sul campo (FPGA), ma purtroppo molti progettisti non conoscono bene le capacità di questi dispositivi e come fare a incorporarle.

Questo articolo descriverà brevemente gli scenari di progettazione che possono trarre beneficio dall'uso degli FPGA. Entrerà quindi nel merito del loro funzionamento e presenterà alcune interessanti soluzioni di FPGA e kit di sviluppo.

Perché usare gli FPGA?

Esiste un'ampia gamma di applicazioni di calcolo, ognuna delle quali può trarre giovamento da un approccio diverso, tra cui microprocessori (MPU) e microcontroller (MCU) di serie, unità di elaborazione grafica (GPU), FPGA e dispositivi System-on-Chip (SoC) personalizzati. Per decidere quale utilizzare, occorre procedere a un'attenta valutazione e a un esame approfondito dei requisiti.

Ad esempio, quando lavorano su tecnologie all'avanguardia come le stazioni base 5G, i progettisti devono tener conto del fatto che gli standard e i protocolli sottostanti sono ancora in evoluzione. Di conseguenza, devono poter rispondere in modo rapido ed efficiente a qualsiasi modifica delle specifiche che sfugge al loro controllo.

Inoltre, devono essere flessibili per rispondere alle future modifiche degli standard e dei protocolli che possono verificarsi dopo l'installazione sul campo dei sistemi. Devono anche essere in grado di rispondere a bug imprevisti nelle funzionalità del sistema o a lacune nella sua sicurezza, modificare le funzionalità esistenti o aggiungerne di nuove per prolungare la vita del sistema.

Un SoC assicura in genere le prestazioni più elevate, ma questo percorso è costoso e richiede tempo. Inoltre, tutti gli algoritmi implementati nella struttura del chip sono essenzialmente "congelati nel silicio". Questa mancanza intrinseca di flessibilità diventa un problema, alla luce delle considerazioni espresse sopra. Per riuscire a coniugare prestazioni ottimali e flessibilità serve un percorso alternativo. Questo percorso spesso viene fornito da FPGA, combinazioni di microprocessori/microcontroller e FPGA, o da FPGA dotati di hard core di processori integrati.

Cosa sono gli FPGA?

Questa è una domanda difficile perché gli FPGA sono molte cose. Inoltre, esistono molti tipi diversi di FPGA, ognuno con diverse combinazioni di capacità e funzioni.

Il cuore di ogni FPGA - l'aspetto che definisce il suo campo d'azione, per così dire - è la sua struttura programmabile, che si presenta come una serie di blocchi a logica programmabile (Figura 1a). Ognuno di questi blocchi logici contiene un insieme di elementi - tra cui una tabella di ricerca (LUT), un multiplexer e un registro - che possono essere configurati (programmati) per comportarsi come richiesto (Figura 2).

Figura 1: Gli FPGA più semplici contengono solo struttura programmabile e GPIO configurabili (a). Architetture diverse potenziano questa struttura fondamentale con blocchi SRAM, PLL e gestori di clock (b), blocchi DSP e interfacce SERDES (c), hard core di processore integrati e periferiche (d). (Immagine per gentile concessione di Max Maxfield)

Figura 1: Gli FPGA più semplici contengono solo struttura programmabile e GPIO configurabili (a). Architetture diverse potenziano questa struttura fondamentale con blocchi SRAM, PLL e gestori di clock (b), blocchi DSP e interfacce SERDES (c), hard core di processore integrati e periferiche (d). (Immagine per gentile concessione di Max Maxfield)

Figura 2: Ogni blocco a logica programmabile contiene un insieme di elementi - tra cui una tabella di ricerca, un multiplexer e un registro - che possono essere configurati (programmati) per comportarsi come richiesto. (Immagine per gentile concessione di Max Maxfield)

Figura 2: Ogni blocco a logica programmabile contiene un insieme di elementi - tra cui una tabella di ricerca, un multiplexer e un registro - che possono essere configurati (programmati) per comportarsi come richiesto. (Immagine per gentile concessione di Max Maxfield)

Molti FPGA utilizzano LUT a 4 ingressi che possono essere configurati per implementare qualsiasi funzione logica a 4 ingressi. Per meglio supportare gli ampi percorsi dati utilizzati in alcune applicazioni, alcuni FPGA offrono LUT a 6, 7 o addirittura 8 ingressi. L'uscita del LUT è collegata direttamente a una delle uscite del blocco logico e a uno degli ingressi del multiplexer. L'altro ingresso al multiplexer è collegato direttamente a un ingresso del blocco logico (e). Il multiplexer può essere configurato per scegliere uno di questi ingressi.

L'uscita del multiplexer alimenta l'ingresso del registro. Ogni registro può essere configurato per funzionare come un flip-flop attivato dai fronti (edge) o come un latch sensibile al livello (detto questo, è sconsigliato usare all'interno di FPGA la logica asincrona sotto forma di latch). Il clock (o abilitazione) di ogni registro può essere configurato per essere attivo alto o attivo basso. Allo stesso modo, può essere configurato anche il livello attivo degli ingressi di impostazione/reset.

Questi blocchi logici possono essere considerati come una sorta di "isole di logica programmabile" mobili in un "mare di interconnessione programmabile". L'interconnessione può essere configurata per collegare qualsiasi uscita da qualsiasi blocco logico a qualsiasi ingresso di altri blocchi logici. Analogamente, gli ingressi primari dell'FPGA possono essere collegati agli ingressi di qualsiasi blocco logico e le uscite di qualsiasi blocco logico possono essere utilizzate per pilotare le uscite primarie del dispositivo.

Per quanto riguarda gli ingressi/le uscite primarie per uso generale (GPIO), sono presentati in banchi (gruppi) e ogni banco può essere configurato per supportare un diverso standard di interfaccia come LVCMOS, LVDS, LVTTL, HSTL o SSTL. Inoltre, è possibile configurare l'impedenza degli ingressi e la velocità di variazione delle uscite.

Il livello successivo della struttura dell'FPGA include blocchi di SRAM, chiamati RAM di blocco (BRAM), circuiti ad aggancio di fase (PLL) e gestore di clock (Figura 1b). È possibile aggiungere anche blocchi di elaborazione dei segnali digitali (DSP) (slice DSP). Contengono moltiplicatori configurabili e un sommatore configurabile che permette loro di eseguire operazioni di moltiplicazione-accumulo (MAC) (Figura 1c).

I blocchi SERDES ad alta velocità - un'altra caratteristica comune degli FPGA - possono supportare interfacce seriali gigabit. È importante notare che non tutti gli FPGA supportano tutte le caratteristiche ricordate sopra. I vari FPGA offrono set di funzionalità diverse mirate a specifici mercati e applicazioni.

La struttura programmabile di un FPGA può essere utilizzata per implementare qualsiasi funzione logica o un insieme di funzioni desiderate, fino al core di processore, o anche core multipli. Se questi core vengono implementati in una struttura programmabile, vengono detti "soft core". A titolo di confronto, alcuni FPGA comunemente chiamati FPGA SoC contengono uno o più processori "hard core", che vengono implementati direttamente nel chip (Figura 1d). Questi hard core di processore possono includere unità a virgola mobile (FPU) e cache L1/L2.

Allo stesso modo, funzioni dell'interfaccia periferica come CAN, I2C, SPI, UART e USB possono essere implementate come soft core nella struttura programmabile, ma molti FPGA li includono come hard core nel chip. Per le comunicazioni tra i core di processore, le funzioni di interfaccia e la struttura programmabile in genere si utilizzano bus ad alta velocità come AMBA e AXI.

I primi FPGA, introdotti sul mercato da Xilinx nel 1985, contenevano solo un array di 8x8 blocchi a logica programmabile (nessun blocco RAM, DSP, ecc.). Gli FPGA di fascia alta odierni, invece, possono contenere centinaia di migliaia di blocchi logici, migliaia di blocchi DSP e megabit di RAM. Complessivamente, possono contenere miliardi di transistor che equivalgono a decine di milioni di gate equivalenti (ad es. gate NAND a 2 ingressi).

Tecnologie di configurazione alternative

Le funzioni dei blocchi logici e l'instradamento dell'interconnessione vengono determinati tramite celle di configurazione, che possono essere considerate come switch 0/1 (off/on). Queste celle sono utilizzate anche per configurare lo standard di interfaccia GPIO, l'impedenza di ingresso, la velocità di variazione dell'uscita, ecc. A seconda dell'FPGA, queste celle di configurazione possono essere implementate utilizzando una delle tre tecnologie seguenti:

- Antifusibile: queste celle di configurazione sono programmabili una sola volta (OTP), il che significa che una volta che il dispositivo è stato programmato non si può tornare indietro. Questi dispositivi tendono a essere limitati ad applicazioni spaziali e ad altre applicazioni ad alta sicurezza. Poiché se ne vendono pochi, hanno un prezzo elevato e sono costosi anche in termini di progettazione.

- Flash: come le celle di configurazione basate su antifusibile, anche quelle basate su flash sono non volatili. Diversamente delle celle antifusibile, le celle flash possono essere riprogrammate a seconda delle necessità. Le celle di configurazione flash sopportano le radiazioni, per cui sono idonee per applicazioni spaziali (anche se con modifiche agli strati superiori di metallizzazione e ai contenitori).

- SRAM: in questo caso, i dati di configurazione vengono memorizzati in una memoria esterna da cui vengono caricati a ogni attivazione dell'FPGA (o come raccomandato nel caso di scenari di configurazione dinamica).

Gli FPGA con celle di configurazione basate su antifusibile o flash hanno il vantaggio di attivarsi immediatamente e di consumare poca energia. Queste tecnologie hanno però lo svantaggio di richiedere ulteriori fasi di elaborazione, oltre al processo CMOS sottostante utilizzato per creare il resto del chip.

Il vantaggio degli FPGA le cui celle di configurazione sono basate sulla tecnologia SRAM è che sono fabbricati utilizzando lo stesso processo CMOS come il resto del chip. Inoltre offrono prestazioni più elevate perché sono in genere di una o due generazioni più avanti rispetto alle tecnologie antifusibile e flash. Gli svantaggi principali delle celle di configurazione SRAM sono un consumo energetico superiore a quello delle loro controparti antifusibile e flash (allo stesso livello tecnologico) e la suscettibilità a disturbi da evento singolo (SEU) causati dalle radiazioni.

Per molto tempo, a causa di questa suscettibilità gli FPGA basati su SRAM sono stati considerati non idonei per applicazioni aerospaziali e spaziali. Ultimamente, sono state impiegate delle speciali strategie di mitigazione, per cui in sistemi come il rover Mars Curiosity oltre agli FPGA basati su flash sono presenti anche quelli basati su SRAM.

Gli FPGA offrono flessibilità

Gli FPGA sono utilizzati per diverse applicazioni. Sono particolarmente utili per implementare funzioni di interfacciamento intelligente, controllo motori, accelerazione algoritmica e calcolo ad alte prestazioni (HPC), elaborazione di immagini e video, visione artificiale, intelligenza artificiale (IA), apprendimento automatico (ML), apprendimento profondo (DL), radar, beamforming, stazioni base e comunicazioni.

Un esempio semplice è quello di fornire un'interfaccia intelligente tra altri dispositivi che utilizzano standard di interfaccia o protocolli di comunicazione diversi. Si consideri un sistema esistente che contiene un processore per applicazioni (AP) collegato a un sensore della telecamera e un dispositivo di visualizzazione che utilizza interfacce legacy (Figura 3a).

Figura 3: Un FPGA può essere utilizzato per fornire un'interfaccia intelligente tra altri dispositivi che utilizzano standard di interfaccia o protocolli di comunicazione diversi, estendendo in tal modo la durata dei progetti esistenti basati su dispositivi legacy. (Immagine per gentile concessione di Max Maxfield)

Figura 3: Un FPGA può essere utilizzato per fornire un'interfaccia intelligente tra altri dispositivi che utilizzano standard di interfaccia o protocolli di comunicazione diversi, estendendo in tal modo la durata dei progetti esistenti basati su dispositivi legacy. (Immagine per gentile concessione di Max Maxfield)

Si supponga ora che chi ha creato il sistema desideri aggiornare il sensore della telecamera e il dispositivo di visualizzazione con qualcosa di più moderno che sia più leggero, meno costoso e che consumi meno energia. L'unico problema è che una o entrambe queste nuove periferiche potrebbero utilizzare un moderno standard di interfaccia che non è supportato dal processore per applicazioni (AP) originale. Oppure, potrebbero supportare un protocollo di comunicazione completamente diverso, come Mobile Industry Processor Interface (MIPI). In questo caso, l'utilizzo di un FPGA con la sua capacità di supportare più standard I/O, abbinato ad alcuni soft core IP MIPI, fornirà un percorso di aggiornamento veloce, economico e privo di rischi (Figura 3b).

Come altro esempio di applicazione, si consideri un'attività ad alta intensità di calcolo come l'elaborazione dei segnali richiesta per implementare un sistema radar, o il beamforming in una stazione base di comunicazione. I processori convenzionali con le loro architetture von Neumann o Harvard sono idonei per certi compiti, ma lo sono meno per quelli che richiedono che venga eseguita ripetutamente la stessa sequenza di operazioni. Questo perché un singolo core di processore che esegue un singolo thread può eseguire solo un'istruzione alla volta (Figura 4a).

Figura 4: A differenza dei microprocessori in cui può essere eseguita una sola istruzione alla volta (in sequenza), in un FPGA si possono eseguire allo stesso tempo (contemporaneamente) più blocchi funzionali. Inoltre, gli FPGA possono implementare algoritmi appropriati in modo massivamente parallelo. (Immagine per gentile concessione di Max Maxfield)

Figura 4: A differenza dei microprocessori in cui può essere eseguita una sola istruzione alla volta (in sequenza), in un FPGA si possono eseguire allo stesso tempo (contemporaneamente) più blocchi funzionali. Inoltre, gli FPGA possono implementare algoritmi appropriati in modo massivamente parallelo. (Immagine per gentile concessione di Max Maxfield)

Nell'FPGA è invece possibile eseguire più funzioni contemporaneamente, il che permette di mettere nella pipeline una serie di operazioni, con un conseguente throughput molto maggiore. Analogamente, invece di eseguire la stessa operazione, ad esempio 1.000 volte su 1.000 coppie di valori di dati con il processore, gli stessi calcoli potrebbero essere eseguiti in maniera massiva e parallela in un singolo ciclo di clock nell'FPGA istanziando 1.000 sommatori nella struttura programmabile (Figura 4b).

Chi produce gli FPGA?

Questo è un mondo in continua evoluzione. I due principali produttori di dispositivi realmente di fascia alta con le capacità e le prestazioni più elevate sono Intel (che ha acquisito Altera) e Xilinx.

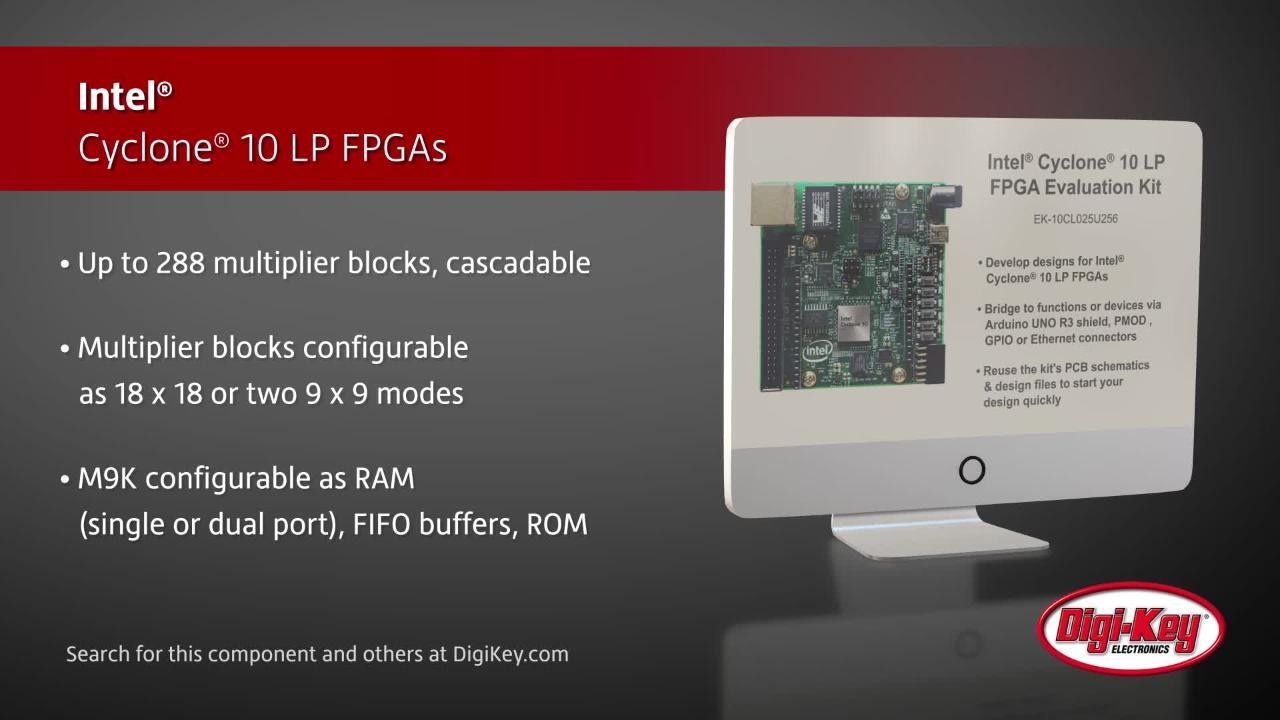

Le offerte di Intel e Xilinx spaziano da FPGA di fascia bassa a FPGA SoC di fascia alta. Un altro fornitore che si occupa quasi esclusivamente di FPGA è Lattice Semiconductor, che punta alle applicazioni di fascia medio-bassa. Infine, ora vi è Microchip Technology che, a seguito dell'acquisizione di Actel, Atmel e Microsemi, sta proponendo numerose famiglie di FPGA di piccole e medie dimensioni e prodotti di fascia bassa della categoria di FPGA SoC.

Data la grande varietà di famiglie, ognuna delle quali offre risorse, prestazioni, capacità e stili di contenitori diversi, scegliere il dispositivo migliore per il compito da svolgere può essere difficile. Ecco alcuni esempi calzanti: dispositivi Intel; dispositivi Lattice Semiconductor e dispositivi Xilinx.

Come progettare con gli FPGA?

Tradizionalmente, per progettare con FPGA gli ingegneri utilizzano un linguaggio di descrizione dell'hardware come Verilog o VHDL per catturare l'obiettivo del progetto. Queste descrizioni possono prima essere simulate per verificare che funzionino come richiesto, dopodiché vengono passate a uno strumento di sintesi che genera il file di configurazione utilizzato per configurare (programmare) l'FPGA.

Ogni fornitore di FPGA sviluppa internamente la propria catena di strumenti oppure offre una versione personalizzata di uno strumento di un fornitore specializzato. In entrambi i casi, gli strumenti sono accessibili dai siti Web dei fornitori di FPGA. Inoltre, possono essere disponibili versioni gratuite o a basso costo di suite complete di strumenti.

Per rendere gli FPGA più accessibili agli sviluppatori di software, alcuni fornitori di FPGA ora offrono strumenti di sintesi di alto livello (HLS). Questi strumenti interpretano una descrizione algoritmica del comportamento desiderato, catturato a un alto livello di astrazione in C, C++ o OpenCL, e generano l'input per alimentare il motore di sintesi di livello inferiore.

Per i progettisti che desiderano mettersi alla prova, esistono molte schede di sviluppo e di valutazione, ognuna delle quali offre capacità e caratteristiche diverse. Tre esempi sono il kit di sviluppo DFR0600 di DFRobot che è dotato di un FPGA SoC Zynq-7000 di Xilinx, DE10 Nano di Terasic con un FPGA SoC Cyclone V di Intel e la scheda di valutazione ICE40HX1K-STICK-EVN con un FPGA iCE40 a basso consumo energetico di Lattice Semiconductor.

I progettisti che pensano di utilizzare una scheda figlia PCIe basata su FPGA per accelerare le applicazioni in esecuzione su una scheda madre X86 potrebbero essere interessati a una delle schede figlie Alveo PCIe di Xilinx.

Conclusione

Spesso le soluzioni di progettazione ottimali sono fornite da FPGA, combinazioni di processori e FPGA o da FPGA dotati di hard core di processore integrati.

Gli FPGA si sono evoluti rapidamente nel corso degli anni e sono in grado di soddisfare numerosi requisiti di progettazione in termini di flessibilità, velocità di elaborazione e potenza, per cui sono utili per un'ampia gamma di applicazioni.

Esonero della responsabilità: le opinioni, le convinzioni e i punti di vista espressi dai vari autori e/o dai partecipanti al forum su questo sito Web non riflettono necessariamente le opinioni, le convinzioni e i punti di vista di DigiKey o le sue politiche.