Nozioni di base sull'analogico: come funzionano i circuiti sample-and-hold e come assicurano la precisione degli ADC

Contributo di Editori nordamericani di DigiKey

2020-04-22

La conversione di un segnale analogico del mondo "reale" in uno digitale che può essere elaborato a monte è una funzione fondamentale di sistemi elettronici che spaziano dalla registrazione audio a Internet delle cose (IoT), Internet delle cose industriale (IIoT) e ora anche l'intelligenza artificiale delle cose (AIoT). Ma, per essere eseguita in modo efficiente ed efficace, occorre comprendere i principi di base e alcuni passaggi che spesso vengono trascurati.

Ad esempio, come viene esattamente "mantenuto" e poi "campionato" un segnale prima della conversione, dato che un tipico segnale analogico applicato all'ingresso di un convertitore analogico/digitale (ADC) cambia continuamente di ampiezza e, alla fine della conversione, sarà diverso da quello iniziale? Questa variazione di ampiezza, o skewing, può causare un grave errore, specialmente nel caso di ADC ad alta risoluzione che richiedono più tempo per convertire un segnale. I progettisti hanno il difficile compito di capire ed eliminare questa fonte di errore.

Questo articolo mostra come evitare lo skew dell'ampiezza utilizzando un circuito sample-and-hold (S/H) o track-and-hold (T/H) per l'ADC. Il circuito S/H (o il T/H) esegue il campionamento vero e proprio dell'ingresso e opera tra il filtro passa-basso antialiasing in ingresso e l'ADC. L'articolo illustra le caratteristiche e i criteri di selezione dei circuiti integrati S/H e prende in esame gli ADC con S/H integrati. A fini illustrativi vengono usati esempi di dispositivi con caratteristiche diverse per applicazioni diverse di Texas Instruments, Maxim Integrated e Analog Devices.

Il ruolo della tecnologia sample-and-hold negli ADC

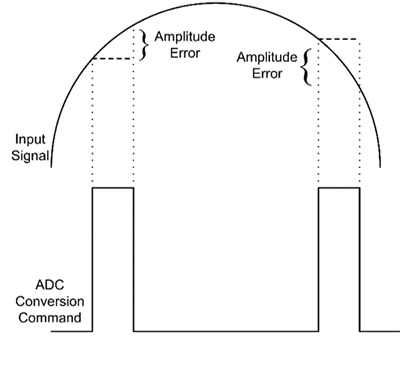

Quando all'ingresso di un ADC viene applicato un segnale non c.c., l'ampiezza cambia continuamente. Tuttavia, il processo di conversione da analogico a digitale richiede un intervallo di tempo finito, durante il quale l'ampiezza dell'ingresso dell'ADC cambierà (Figura 1). Questo skewing dell'ampiezza si traduce in un errore potenzialmente grave.

Figura 1: Un ADC con un segnale di ingresso variabile è soggetto a errori di ampiezza (in alto) dovuti alle variazioni di ampiezza del segnale durante la digitalizzazione (in basso). (Immagine per gentile concessione di DigiKey)

Figura 1: Un ADC con un segnale di ingresso variabile è soggetto a errori di ampiezza (in alto) dovuti alle variazioni di ampiezza del segnale durante la digitalizzazione (in basso). (Immagine per gentile concessione di DigiKey)

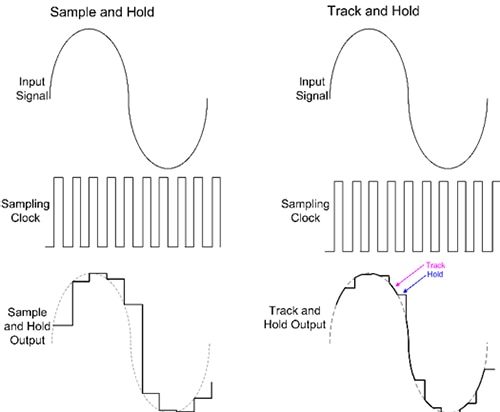

Per evitare lo skew dell'ampiezza in un ADC è necessario campionare il segnale e mantenere un'ampiezza fissa mentre è in atto la conversione. Il circuito S/H o T/H per l'ADC serve esattamente a questo scopo (Figura 2).

Figura 2: La differenza principale tra un circuito S/H (a sinistra) e uno T/H (a destra) è la durata del periodo di tracciamento: è breve in S/H e lungo in T/H. (Immagine per gentile concessione di DigiKey)

Figura 2: La differenza principale tra un circuito S/H (a sinistra) e uno T/H (a destra) è la durata del periodo di tracciamento: è breve in S/H e lungo in T/H. (Immagine per gentile concessione di DigiKey)

Entrambi i tipi di circuiti campionano il segnale di ingresso e mantengono costante la tensione campionata per la durata del processo di conversione. L'uscita del circuito T/H (a destra) traccia il segnale di ingresso finché non viene segnalato di effettuare il campionamento, quindi mantiene il valore di campionamento durante la conversione ADC. Il circuito S/H ha un'apertura di campionamento più breve e la sua uscita è una serie di livelli campionati (a sinistra). La differenza chiave tra T/H e S/H è la durata dell'intervallo di tracciamento: molto breve nel caso di S/H e molto più lunga nel caso di T/H. Entrambi i circuiti si basano su un commutatore veloce per isolare un condensatore di immagazzinaggio che è stato collegato all'ingresso del segnale. Il questo articolo il termine S/H verrà utilizzato anche per indicare T/H.

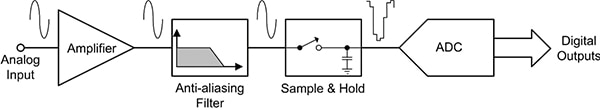

Lo stadio S/H esegue il campionamento vero e proprio dell'ingresso e opera tra il filtro passa-basso antialiasing in ingresso e l'ADC. Il filtro passa-basso esegue la limitazione della banda di antialiasing e, per evitare l'aliasing, deve precedere l'S/H per limitare la banda del segnale prima del campionamento (Figura 3).

Figura 3: Nel percorso del segnale del digitalizzatore, il circuito S/H viene messo tra il filtro passa-basso antialiasing e l'ADC. (Immagine per gentile concessione di DigiKey)

Figura 3: Nel percorso del segnale del digitalizzatore, il circuito S/H viene messo tra il filtro passa-basso antialiasing e l'ADC. (Immagine per gentile concessione di DigiKey)

Tenere presente che i segnali prima dell'S/H sono tutti analogici. L'uscita dell'S/H è una forma d'onda campionata che viene inviata all'ADC.

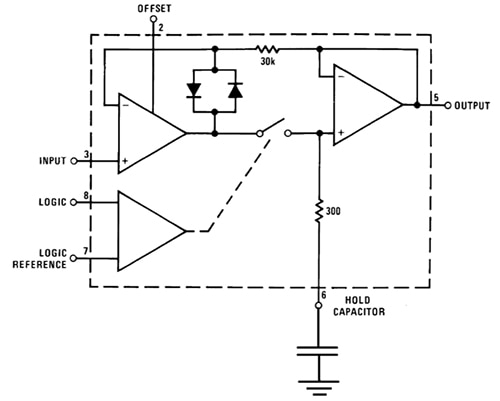

Un tipico dispositivo S/H

Il diagramma a blocchi del circuito integrato S/H LF398MX/NOPB di Texas Instruments mostra la configurazione circuitale di base (Figura 4). Il circuito S/H viene implementato con un commutatore veloce e un condensatore di alta qualità. Nel caso di LF398MX/NOPB, il condensatore è esterno al CI. Quando il commutatore è chiuso, il condensatore viene caricato al livello di tensione del segnale di ingresso. Quando il commutatore è aperto, il condensatore mantiene quella tensione finché non viene digitalizzata dall'ADC. Questo S/H utilizza la tecnologia bi-FET, che combina dei FET con transistor bipolari, per supportare un'acquisizione veloce (inferiore a 6 microsecondi (µs) con un errore di ampiezza dello 0,01%), con una precisione c.c. elevata (tipicamente dello 0,002%) e un abbassamento di tensione estremamente contenuto (in genere inferiore a 83 µV al secondo). Gli amplificatori interni bufferizzano il commutatore e mantengono il condensatore.

Il tempo di acquisizione dell'S/H dipende dal valore del condensatore di mantenimento, che può essere nell'intervallo tra 0,001 e 0,1 µF. Il condensatore di mantenimento esterno deve avere un basso assorbimento dielettrico e una bassa dispersione. Si consigliano condensatori in polistirene, polipropilene e teflon.

Figura 4: Il diagramma a blocchi dell'S/H LF398MX/NOPB di Texas Instruments mostra i componenti chiave: un commutatore veloce e un condensatore di mantenimento esterno. (Immagine per gentile concessione di Texas Instruments)

Figura 4: Il diagramma a blocchi dell'S/H LF398MX/NOPB di Texas Instruments mostra i componenti chiave: un commutatore veloce e un condensatore di mantenimento esterno. (Immagine per gentile concessione di Texas Instruments)

Caratteristiche delle reti S&H

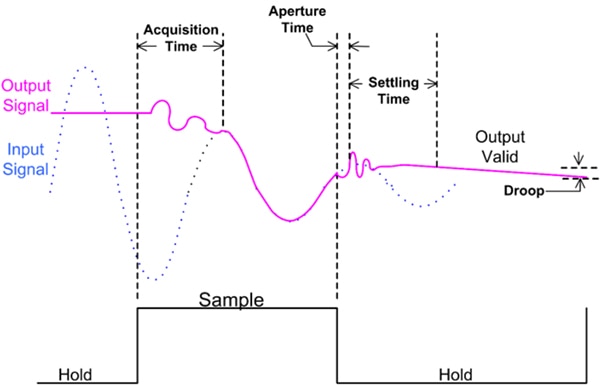

I dispositivi S/H hanno una serie di termini specifici per descrivere il loro funzionamento (Figura 5).

Figura 5: Le definizioni delle caratteristiche dinamiche di un S/H comune includono il tempo di acquisizione, il tempo di assestamento, il tempo di apertura e una riduzione di ampiezza. (Immagine per gentile concessione di DigiKey)

Figura 5: Le definizioni delle caratteristiche dinamiche di un S/H comune includono il tempo di acquisizione, il tempo di assestamento, il tempo di apertura e una riduzione di ampiezza. (Immagine per gentile concessione di DigiKey)

Il tempo di acquisizione è il tempo che intercorre dalla commutazione in modalità campionamento fino al momento in cui l'S/H inizia a tracciare il segnale di ingresso. Dipende dal valore del condensatore di mantenimento e dalla resistenza in serie al commutatore e del percorso del segnale. Quando la modalità torna a mantenimento, potrebbe esserci un ritardo finché il dispositivo non smette di tracciare l'ingresso e inizia a mantenere un valore: questo è il tempo di apertura. Il tempo di apertura dipende dai ritardi di propagazione dei driver e del commutatore. L'incertezza di apertura o jitter è la variazione del tempo di apertura dovuta alle variazioni del clock e al rumore.

Una volta in modalità di mantenimento, intercorre un certo tempo tra l'ingresso in tale modalità e il momento in cui il dispositivo si assesta all'interno di una banda di errore sul valore di mantenimento chiamato assestamento o tempo di assestamento. Una parte del tempo di assestamento può includere un trasferimento di carica indesiderato tra il driver del commutatore e il condensatore di mantenimento; questo è detto errore di mantenimento. Le grandezze del passo di mantenimento di solito sono nell'ordine dei millivolt. L'effetto viene ridotto al minimo mantenendo il più alto possibile l'intervallo di fondo scala dei segnali.

Il periodo di campionamento più breve per l'S/H è la somma del tempo di acquisizione, del tempo di apertura e del tempo di assestamento. Il tempo di campionamento massimo possibile è il reciproco della somma del tempo di acquisizione, del tempo di apertura e del tempo di assestamento.

Durante la modalità di mantenimento, il valore di mantenimento dell'S/H potrebbe scendere a causa di perdite dal condensatore di mantenimento. Questo incremento della tensione è detto abbassamento di tensione. Di solito l'abbassamento è indicato in mV al secondo.

Configurazioni dell'S/H

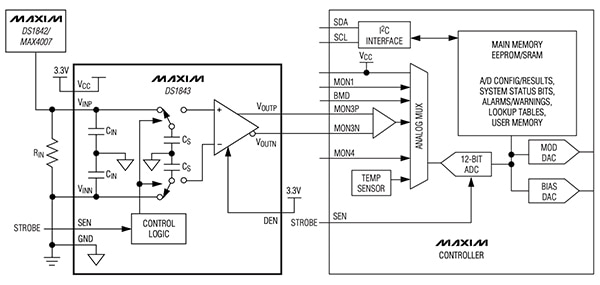

I circuiti integrati dell'S/H sono disponibili in molte configurazioni in funzione delle esigenze applicative. Si consideri un'applicazione che richiede ingressi differenziali come l'interfacciamento con un trasduttore di uscita differenziale come un accelerometro, un estensimetro o un monitor di corrente ottico. DS1843D+TRL di Maxim Integrated è un buon esempio di un CI S/H per queste applicazioni (Figura 6).

Figura 6: Come mostrato in questo circuito operativo tipico, DS1843+TRL di Maxim Integrated è un S/H differenziale che usa doppi condensatori di mantenimento per implementare il campionamento differenziale. (Immagine per gentile concessione di Maxim Integrated)

Figura 6: Come mostrato in questo circuito operativo tipico, DS1843+TRL di Maxim Integrated è un S/H differenziale che usa doppi condensatori di mantenimento per implementare il campionamento differenziale. (Immagine per gentile concessione di Maxim Integrated)

DS1843+TRL è usato in una tipica applicazione di trasmissione di una linea ottica per la misurazione dell'indicatore dell'intensità del segnale ricevuto (RSSI) in modalità burst. DS1842/MAX4007 di Maxim Integrated è un monitor di corrente che riflette la corrente da un fotodiodo a valanga collegato al suo ingresso di riferimento. La corrente di uscita viene indirizzata attraverso il resistore, RIN, che la converte in tensione. Questa tensione viene misurata in modo differenziale da DS1843, che è costituito da commutatori di campionamento totalmente differenziale e da condensatori, CS, oltre a un buffer di uscita differenziale. Questo S/H utilizza due condensatori da 5 pF, uno collegato all'ingresso differenziale positivo e l'altro all'ingresso differenziale negativo. Il basso valore di capacità assicura un tempo di acquisizione veloce. Questo dispositivo ha un tempo di campionamento veloce (acquisizione) inferiore a 300 ns. Il tempo di mantenimento dell'S/H è superiore a 100 µs.

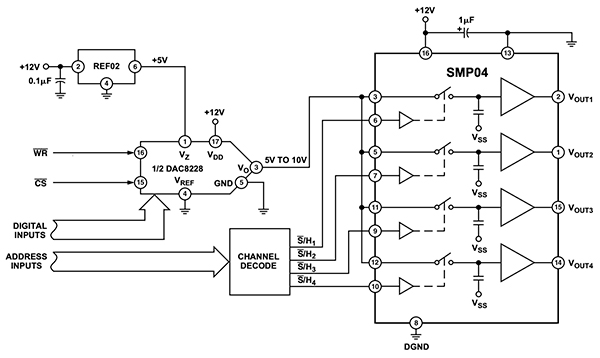

Sono disponibili dispositivi che contengono quattro o otto circuiti S/H in un unico contenitore CI. Ne è un esempio il quad S/H SMP04ESZ-REEL di Analog Devices. SMP04ESZ-REEL è un dispositivo CMOS che comprende quattro circuiti S/H in un normale contenitore. Ha un tempo di acquisizione di 7 µs e una velocità di abbassamento di tensione di soli 2 mV/s (Figura 7).

La Figura 7 illustra anche come usare gli S/H con i convertitori digitale/analogico (DAC), in questo caso per evitare transitori in uscita o glitch causati da transizioni di codice nel DAC.

Figura 7: Il quad S/H SMP04 di Analog Devices contiene quattro circuiti S/H indipendenti e i rispettivi amplificatori buffer. Il circuito mostrato utilizza SMP04 per multiplare l'uscita di un DAC in quattro canali. (Immagine per gentile concessione di Analog Devices)

Figura 7: Il quad S/H SMP04 di Analog Devices contiene quattro circuiti S/H indipendenti e i rispettivi amplificatori buffer. Il circuito mostrato utilizza SMP04 per multiplare l'uscita di un DAC in quattro canali. (Immagine per gentile concessione di Analog Devices)

Nella figura, SMP04 è usato per multiplare l'uscita di un DAC, suddividendola in quattro canali multiplati. I circuiti S/H possono essere usati per ritardare selettivamente l'uscita del DAC fino a dopo il "glitch", livellandola.

Per aumentare il throughput di un ADC si possono utilizzare più circuiti S/H mettendo gli ingressi multiplati in una pipeline. Qui, più S/H sono collegati in comune all'uscita del multiplexer. L'ADC è collegato a un S/H, che mantiene il livello d'ingresso per una conversione. Gli altri S/H acquisiscono altri canali multiplexer e, a loro volta, si collegano all'ADC, mentre il primo S/H è libero di collegarsi a un altro canale multiplato. Questa tecnica di pipelining elimina il tempo di acquisizione dell'S/H nel percorso del segnale dell'ADC.

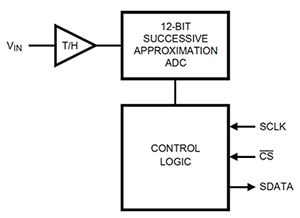

Molti ADC incorporano circuiti S/H o T/H all'interno del loro contenitore integrato. Ne è un esempio ADC121S021CIMFX di Texas Instruments, un ADC con registro ad approssimazioni successive (SAR) a 12 bit con T/H incorporato che opera con frequenze di campionamento tra 50 e 200 ksps. È dotato di un bus di uscita seriale ad alta velocità che semplifica il layout del cablaggio (Figura 8).

Figura 8: Schema di ADC121S021 di Texas Instruments, un ADC SAR a canale singolo a 12 bit con un circuito T/H integrato. (Immagine per gentile concessione di Texas Instruments)

Figura 8: Schema di ADC121S021 di Texas Instruments, un ADC SAR a canale singolo a 12 bit con un circuito T/H integrato. (Immagine per gentile concessione di Texas Instruments)

Questo ADC è tipico di molti circuiti ADC integrati in quanto ha un T/H interno che semplifica il layout della scheda e aiuta a ridurre al minimo il numero di componenti. I circuiti T/H esterni sono utilizzati per configurazioni speciali, come connessioni a ingresso differenziale, ingressi multiplati, o quando l'ADC non ha un circuito T/H o S/H interno.

Conclusione

Dalla registrazione audio alla più avanzata analisi IIoT o IA, la funzione elettronica più elementare della conversione di un segnale analogico in uno digitale richiede un'attenzione particolare ai circuiti S/H o T/H. Questi circuiti sono fondamentali per ridurre al minimo gli errori di distorsione di skew durante il processo di conversione analogico/digitale, poiché mantengono costante la tensione di ingresso all'ADC durante la conversione. Il circuito S/H può essere interno all'ADC o esterno, ma deve trovarsi nel percorso del segnale tra il filtro passa-basso antialiasing e l'ADC. Come è stato dimostrato, esistono molte configurazioni - dispositivi singoli, differenziali o multipli per CI - per soddisfare numerose applicazioni di progettazione. Queste applicazioni si estendono fino a comprendere la prevenzione dei transitori di uscita o dei glitch causati dalle transizioni di codice nei DAC.

Letture consigliate

Esonero della responsabilità: le opinioni, le convinzioni e i punti di vista espressi dai vari autori e/o dai partecipanti al forum su questo sito Web non riflettono necessariamente le opinioni, le convinzioni e i punti di vista di DigiKey o le sue politiche.