Principi base del mondo analogico - Parte 4: Ottimizzazione degli ADC delta-sigma per il basso rumore

Contributo di Editori nordamericani di DigiKey

2020-08-05

Nota del redattore: I convertitori analogico/digitale (ADC) collegano il mondo analogico a quello digitale e sono quindi fondamentali in qualsiasi sistema elettronico connesso al mondo reale. Svolgono un ruolo determinante anche per le prestazioni di un sistema. Questa serie illustra nei dettagli i fondamenti degli ADC, i vari tipi e le rispettive applicazioni. La Parte 1 di questa serie tratta dei principi base del mondo analogico relativi agli ADC SAR. La Parte 2 prende in esame i convertitori delta-sigma. La Parte 3 esamina gli ADC pipeline. Questa Parte 4 mostra come gli ADC delta-sigma possono generare risultati di rumore ultrabasso. La Parte 5 esplora i problemi di pilotaggio dell'ingresso che affliggono gli ADC SAR.

La topologia dei circuiti integrati delta-sigma (ΔƩ) continua ad essere presente nei convertitori analogico/digitali (ADC), generando soluzioni ad alta risoluzione, ad alta integrazione e a bassa potenza per le applicazioni di controllo di processi, misurazione precisa della temperatura e pesatura.

Ciò che disorienta su questo tipo di convertitore è che inizia con una conversione a 1 bit con un rapporto teorico segnale/rumore (SNR) di 7,78 dB, equivalente a 2 volt (VRMS) di rumore in un sistema a 5 V. Da lì, l'ADC può diventare un autentico convertitore delta-sigma a 24 bit che fornisce un SNR teorico di 146 dB, equivalente a 244 nV di rumore rms in un sistema a 5 V.

Questo salto di risoluzione da 1 a 24 bit si basa su algoritmi di sovracampionamento, modulatori di modellazione del rumore e filtri digitali per abbassare il rumore di quantizzazione e aumentare l'SNR. Esiste un modo per evitare la complessità del convertitore ΔƩ e il rumore associato, utilizzando uno stadio di ingresso dell'amplificatore che alimenta un ADC con registro ad approssimazione successiva (SAR) a 12 o 16 bit. Questo percorso di progettazione funzionerà, ma richiede più circuiti integrati sulla scheda CS e più componenti in distinta base.

C'è un modo migliore per risolvere il problema del rumore: affrontarlo a testa alta con un ADC ΔƩ a bassissimo rumore.

Questo articolo tratta brevemente l'applicazione finale a basso rumore e spiega come un ADC ΔƩ è progettato internamente per soddisfare questo requisito. Presenta poi due ADC ΔƩ di Texas Instruments: uno che enfatizza la precisione a 24 bit, l'altro la precisione a 32 bit, mostrando come sfruttare in entrambi il robusto filtraggio digitale.

Dove è adatto un ADC ΔƩ

Da un punto di vista analogico, gli ingegneri richiedono vari gradi di precisione quando misurano l'uscita di temperatura, pressione, celle di carico e sensori ottici. Gli amplificatori migliorano la capacità dei progettisti di quantificare eventi analogici di natura piccola e nella maggior parte dei casi vicino alla corrente continua. La progressiva digitalizzazione ha deterinato un cambiamento di prospettiva e di capacità, migliorando al contempo la capacità di memorizzare e modificare i segnali dei sensori.

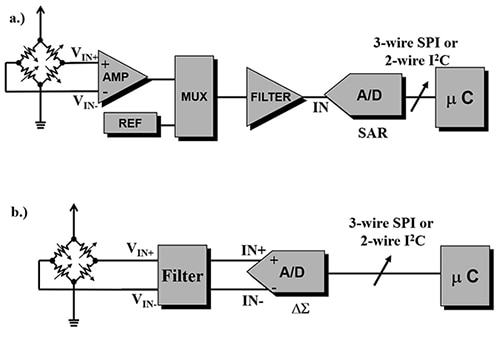

Un tipico percorso del segnale di un sensore verso l'acquisizione digitale inizia con il sensore, passa per gli stadi di guadagno, multiplexing e filtraggio e poi verso l'ADC (Figura 1a).

Figura 1: Due tecniche per digitalizzare il segnale di un sensore utilizzano gli ADC SAR (a) o gli ADC ΔƩ (b). Per i circuiti ad alta risoluzione, l'ADC SAR richiede l'amplificazione e un filtro attivo del quinto ordine, mentre l'ADC ΔƩ richiede un filtro passivo analogico di primo ordine di tipo front-end. (Immagine da A Baker’s Dozen: Real Analog Solutions for Digital Designers, B. Baker, ISBN 0-7506-7819-4)

Figura 1: Due tecniche per digitalizzare il segnale di un sensore utilizzano gli ADC SAR (a) o gli ADC ΔƩ (b). Per i circuiti ad alta risoluzione, l'ADC SAR richiede l'amplificazione e un filtro attivo del quinto ordine, mentre l'ADC ΔƩ richiede un filtro passivo analogico di primo ordine di tipo front-end. (Immagine da A Baker’s Dozen: Real Analog Solutions for Digital Designers, B. Baker, ISBN 0-7506-7819-4)

Il convertitore nella Figura 1a è un ADC SAR capace di eseguire conversioni da 12 a 18 bit e di funzionare a velocità di conversione fino a 10 megacampioni al secondo (Msps). Il convertitore a 16 bit fornisce 216 o 65.536 segmenti. In un sistema a 5 V, il bit meno significativo (LSB) è 5 V/216298 o 76,3 mV, con un SNR teorico pari a 98 dB. Una maggiore granularità è possibile esercitando il guadagno analogico prima del convertitore SAR.

La catena di segnali ΔƩ (Figura 1b) migliora la risoluzione con un unico convertitore, che riduce anche il numero di componenti in distinta base. L'ADC ΔƩ può fornire conversioni da 16 bit a 32 bit. In questa catena di segnali, l'ADC ΔƩ a 24 bit fornisce 224 o 16.777.216 segmenti. In un sistema a 5 V, l'LSB è quindi 5 V/224, o 298 nV, con un SNR teorico pari a 146 dB. Questo livello di risoluzione avvicina la granularità del convertitore alle capacità del sensore.

L'ADC ΔƩ a 24 bit è più lento a causa dei filtri digitali interni che richiedono tempo per implementare i calcoli di filtraggio. Le tipiche velocità dei dati in uscita di questo convertitore vanno da pochi hertz a 1 Msps. Si noti che il filtro analogico è ora un economico filtro resistore-condensatore (RC) di primo ordine al posto del complesso filtro analogico di quinto ordine con tre amplificatori operazionali.

Le differenze tra il rumore di questi due approcci sono evidenti: l'ADC ΔƩ a basso rumore supera l'ADC SAR (Tabella 1).

*Nota: SNR = 6,02 N + 1,76, dove N è il numero di bit

|

Tabella 1: Segmenti ADC, LSB e SNR teorico con tensione di ingresso a fondo scala di 5 V per un ADC SAR a 16 bit e ADC ΔƩ a 24 bit. (Dati per gentile concessione di DigiKey)

L'ADC ΔƩ è una soluzione eccellente per le applicazioni con sensori di temperatura, pressione e celle di carico, dove la specifica della velocità non è critica ma la precisione è fondamentale. Questo ADC può convertire questi piccoli valori di tensione utilizzando tecniche di riduzione del rumore digitali e non analogiche.

Uno sguardo all'interno di un ADC ΔƩ

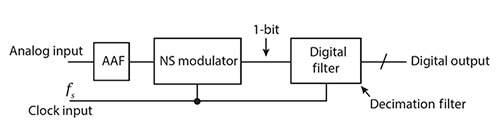

L'interno di un ADC ΔƩ è per l'80% digitale. Tipicamente, il convertitore riceve il segnale di ingresso e converte immediatamente tale segnale analogico in digitale. Il convertitore combina quindi quel segnale digitale con le successive conversioni del modulatore in uno stadio di filtraggio digitale in cui il segnale a 1 bit accumulato viene cambiato in bit multipli. Il convertitore invia poi in serie la conversione finale multi-bit al microcontroller in attesa, attraverso lo stadio di uscita digitale.

Il segnale analogico passa prima attraverso un filtro antialiasing (AAF) esterno di primo ordine. Poi il modulatore di modellazione del rumore (NS) prende il segnale analogico e genera un flusso di 1 bit alla velocità di clock del convertitore nel filtro digitale (Figura 2).

Figura 2: Il tipico ADC ΔƩ passa il segnale analogico attraverso un AAF di primo ordine, genera un flusso di 1 bit utilizzando il modulatore NS, quindi produce un risultato multi-bit all'uscita digitale verso un microcontroller. (Immagine da CMOS: Mixed-Signal Circuit Design, 2nd Edition, J. Baker, ISBN 978-0-470-29026-2)

Figura 2: Il tipico ADC ΔƩ passa il segnale analogico attraverso un AAF di primo ordine, genera un flusso di 1 bit utilizzando il modulatore NS, quindi produce un risultato multi-bit all'uscita digitale verso un microcontroller. (Immagine da CMOS: Mixed-Signal Circuit Design, 2nd Edition, J. Baker, ISBN 978-0-470-29026-2)

Il filtro digitale riceve più codici dal flusso a 1 bit e crea un risultato completo multi-bit nel filtro digitale. Questi risultati multi-bit sono trasmessi in serie attraverso l'uscita digitale.

Il modulatore ΔƩ

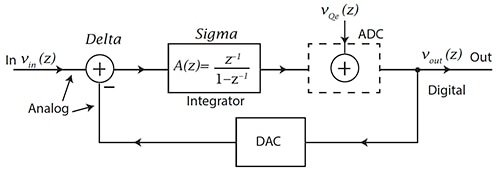

Il numero di anelli integratore/retroazione determina l'ordine del modulatore ΔƩ. Il modulatore ADC ΔƩ di primo ordine ha un singolo integratore e un anello di retroazione (Figura 3).

Figura 3: Modulatore del primo ordine con un integratore analogico e un ADC a 1 bit e un DAC nell'anello di retroazione. VQe(z) è il rumore di quantizzazione dell'ADC. (Immagine da CMOS: Mixed-Signal Circuit Design, 2nd Edition, J. Baker, ISBN 978-0-470-29026-2)

Figura 3: Modulatore del primo ordine con un integratore analogico e un ADC a 1 bit e un DAC nell'anello di retroazione. VQe(z) è il rumore di quantizzazione dell'ADC. (Immagine da CMOS: Mixed-Signal Circuit Design, 2nd Edition, J. Baker, ISBN 978-0-470-29026-2)

Nella Figura 3, il segnale analogico (VIN(z)) entra nella porzione delta (Δ) del modulatore. Il segnale analogico passa poi attraverso uno stadio integratore o stadio sigma (Ʃ) a un ADC a 1 bit (con una frequenza di campionamento di fS, secondo la Figura 2), che può essere un comparatore. Questo segnale digitalizzato si ritrasmette al convertitore digitale/analogico (DAC) a 1 bit e procede anche al VOUT(z) nello stadio Δ. Il DAC a 1 bit ha una tensione analogica che deve essere sottratta dal segnale di ingresso analogico, VIN(z). La funzione di trasferimento di questo modulatore di primo ordine è:

![]() Equazione 1

Equazione 1

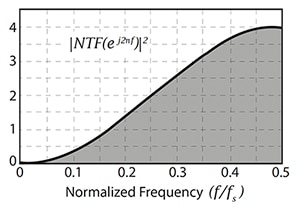

A causa dell'integratore e dell'anello di retroazione, il modulatore implementa un algoritmo di modellazione del rumore sul flusso dei dati di uscita digitale del modulatore (Figura 4).

Figura 4: La funzione di modellazione del rumore all'uscita del modulatore ΔƩ, dove la funzione di trasferimento del rumore (NTF) è uguale a 1-z-1, dove la frequenza normalizzata 0,5 è uguale a FS/2. (Immagine da Understanding Delta-Sigma Data Converters, Schreier, Temes, ISBN 0-471-46585-2)

Figura 4: La funzione di modellazione del rumore all'uscita del modulatore ΔƩ, dove la funzione di trasferimento del rumore (NTF) è uguale a 1-z-1, dove la frequenza normalizzata 0,5 è uguale a FS/2. (Immagine da Understanding Delta-Sigma Data Converters, Schreier, Temes, ISBN 0-471-46585-2)

Nella Figura 4, la caratteristica di modellazione del rumore è il primo passo verso la riduzione del rumore di quantizzazione a 1 bit di conversione. Con il rumore nelle frequenze più alte, un filtro digitale passa-basso completa il processo di riduzione del rumore.

I modulatori di ordine superiore contengono integratori e anello di retroazione aggiuntivi. Ad esempio, un modulatore del terzo ordine ha tre integratori e tre anelli di retroazione. La funzione di modulazione del rumore cambia con l'ordine del modulatore riducendo il rumore vicino a c.c. e aumentando il rumore modellato.

I modulatori di ordine superiore offrono prestazioni migliori a scapito di maggior hardware al silicio, stabilità ridotta e intervallo di segnale.

Filtri digitali ΔƩ

L'ADC ΔƩ funziona con il sovracampionamento (OS), ossia il rapporto tra la frequenza di campionamento del modulatore (FS) e la velocità dei dati in uscita dell'ADC (FD), secondo l'equazione 2:

![]() Equazione 2

Equazione 2

Il sovracampionamento migliora il rumore dell'ADC ΔƩ grazie alla larghezza di banda digitale che limita i dati modellati del rumore con uno o più filtri digitali passa-basso.

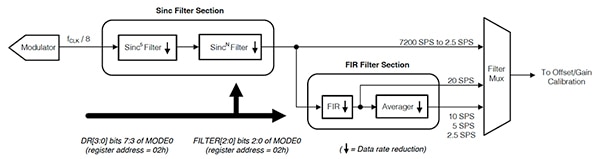

I due filtri digitali comunemente usati nell'ADC ΔƩ sono filtri sin(pf)/pf (sinc) e filtri a risposta impulsiva finita (FIR). L'implementazione del filtro digitale in ADS1235di Texas Instruments, un ADC ΔƩ a 24 bit e negli ADC ΔƩ a 32 bit ADS1262 e ADS1263 (ADS1263 integra un ADC ΔƩ a 24 bit ausiliario destinato alle misurazioni in background), consente di scegliere se utilizzare esclusivamente i filtri sinc oppure una combinazione di filtri sinc e FIR (Figura 5).

Figura 5: L'ADC ΔƩ a 24 bit ADS1235 offre l'uso esclusivo dei filtri sinc o una combinazione di filtri sinc e FIR. (Immagine per gentile concessione di Texas Instruments)

Figura 5: L'ADC ΔƩ a 24 bit ADS1235 offre l'uso esclusivo dei filtri sinc o una combinazione di filtri sinc e FIR. (Immagine per gentile concessione di Texas Instruments)

Nella Figura 5, il filtro sinc (indicato con "Sinc") è un filtro digitale passa-basso. L'uscita (w(n)) di un filtro sinc viene calcolata con l'equazione 3:

![]() Equazione 3

Equazione 3

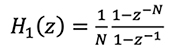

La funzione di trasferimento del dominio z è:

Equazione 4

Equazione 4

La risposta in frequenza è:

![]() Equazione 5

Equazione 5

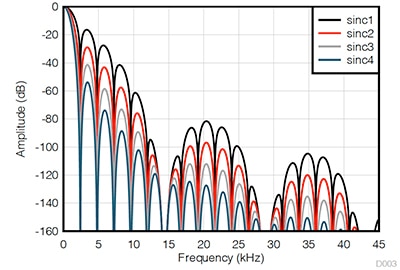

Nella Figura 5, SincN equivale a N filtri sinc identici in serie. L'ampiezza grafica rispetto alla risposta in frequenza del filtro sinc ha un aspetto simile a un pettine (Figura 6).

Figura 6: In ADS1262/63, a 2400 campioni al secondo i numerosi filtri digitali sinc - dove sinc2 è equivalente a due filtri SINC identici in serie e sinc3 è equivalente a tre filtri sinc identici in serie, ecc. - crea la risposta in frequenza con una forma simile a un pettine. (Immagine per gentile concessione di Texas Instruments)

Figura 6: In ADS1262/63, a 2400 campioni al secondo i numerosi filtri digitali sinc - dove sinc2 è equivalente a due filtri SINC identici in serie e sinc3 è equivalente a tre filtri sinc identici in serie, ecc. - crea la risposta in frequenza con una forma simile a un pettine. (Immagine per gentile concessione di Texas Instruments)

Nella Figura 6, i picchi e i nulli sono caratteristici della risposta del filtro sinc. I nulli della risposta in frequenza si verificano a f (Hz) = N FD, dove N = 1, 2, 3, ... Alle frequenze nulle, il filtro ha un guadagno pari a zero.

I filtri sinc (in serie) creano una maggiore attenuazione, causando una maggiore latenza. Ad esempio, se un calcolo specifico del filtro sinc con una frequenza di clock esterna di 7,3728 MHz produce una velocità dei dati in uscita di 14400 sps, la velocità dei dati in uscita del secondo filtro sinc è di 7200 sps.

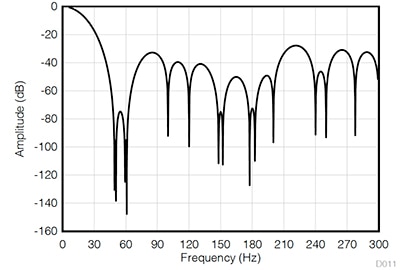

Il filtro FIR passa-basso è un filtro basato su coefficienti. Il filtro ha un'attenuazione simultanea di 50 Hz e 60 Hz e armoniche a una velocità dati da 2,5 sps a 20 sps. Il tempo di latenza di conversione delle velocità dati del filtro FIR è equivalente a un singolo ciclo. Il filtro FIR riceve i dati pre-filtrati dal filtro sinc e li decima per produrre le velocità dei dati in uscita di 10 sps (Figura 7).

Figura 7: In ADS1262/63, il filtro FIR attenua i segnali a 50 Hz e 60 Hz per ridurre le interferenze della frequenza di linea e fornisce una serie di nulli di risposta posti vicino a queste frequenze. I nulli si ripetono alle armoniche a 50 Hz e 60 Hz. (Immagine per gentile concessione di Texas Instruments)

Figura 7: In ADS1262/63, il filtro FIR attenua i segnali a 50 Hz e 60 Hz per ridurre le interferenze della frequenza di linea e fornisce una serie di nulli di risposta posti vicino a queste frequenze. I nulli si ripetono alle armoniche a 50 Hz e 60 Hz. (Immagine per gentile concessione di Texas Instruments)

Il filtro FIR attenua i segnali a 50 Hz e 60 Hz per ridurre l'interferenza delle frequenze di linea e fornisce una serie di nulli di risposta posti vicino a queste frequenze. La risposta si ripete alle armoniche a 50 Hz e 60 Hz.

Un ADC ΔƩ preciso e silenzioso

Un ottimo esempio di ADC ΔƩ a basso rumore è il già menzionato convertitore a 24 bit con ingresso differenziale ADS1235 di Texas Instruments.

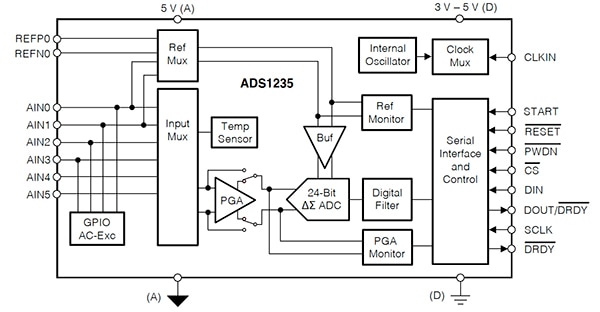

ADS1235 è un ADC ΔƩ di precisione, 7200 sps, con tre ingressi differenziali o cinque ingressi a terminazione singola e un amplificatore a guadagno programmabile (PGA) integrato con guadagni di 1, 64 e 128. Questo dispositivo include anche funzionalità diagnostiche come monitor di riferimento e PGA fuori intervallo. L'ADC fornisce dati di conversione a deriva zero ad alta precisione per apparecchiature di alta precisione come bilance, estensimetri e sensori di pressione resistivi (Figura 8).

Figura 8: Diagramma a blocchi dell'ADC ΔƩ a 24 bit ADS1235 con ingresso analogico a sei canali e multiplexer di ingresso GPIO. (Immagine per gentile concessione di Texas Instruments)

Figura 8: Diagramma a blocchi dell'ADC ΔƩ a 24 bit ADS1235 con ingresso analogico a sei canali e multiplexer di ingresso GPIO. (Immagine per gentile concessione di Texas Instruments)

Per ADS1235, i fattori significativi che influenzano le prestazioni di rumore sono la velocità di trasmissione dati, il guadagno PGA e la modalità chopping. Le velocità dati minori introducono la frequenza d'angolo del filtro digitale, riducendo così il rumore. Inoltre, a causa di una media dei dati a due punti, eseguita in modalità chopping, il rumore diminuisce di √2 rispetto al funzionamento normale.

Con una bassa frequenza, una velocità dati di 2,5 sps e un guadagno PGA di 1 V/V, il rumore del convertitore all'uscita digitale sinc3 in un sistema a 5 V è di 0,15 mVRMS (0,3 mV picco-picco (PP)) con una risoluzione efficace di 24 bit, così come una risoluzione senza rumore di 24 bit. L'SNR teorico, oltre che efficace, di questo dispositivo è di 146 dB. Infatti, in queste condizioni, il modulatore stabile di quarto ordine e i filtri da sinc1 a sinc4 producono una risoluzione efficace di 24 bit, oltre a una risoluzione senza rumore di 24 bit.

ADS1235 ha realizzato conversioni a 24 bit quasi perfette per una velocità dati di 2,5 sps. La prossima generazione di ADC ΔƩ in questa famiglia di Texas Instruments è data dai dispositivi ADS1262/63. La differenza principale tra questi dispositivi è che ADS1262/63 migliora la circuiteria a basso rumore e offre un registro dati di uscita esteso a 32 bit.

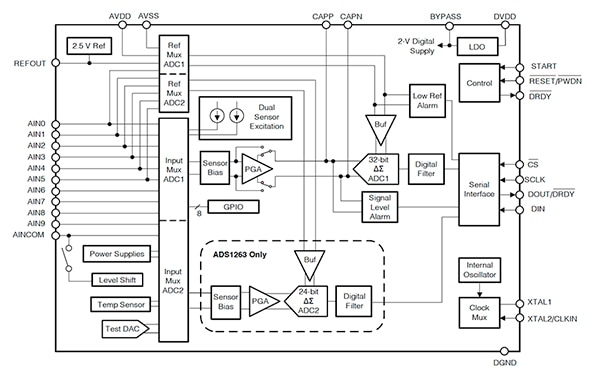

ADS1262/63 ha un PGA CMOS migliorato a basso rumore con guadagni di 1, 2, 4, 8, 16 e 32. Il front-end analogico (AFE) flessibile incorpora due sorgenti di corrente per l'eccitazione del sensore idonee per le misurazioni dirette di RTD (Figura 9).

Figura 9: Diagramma a blocchi dell'ADC ΔƩ a 32 bit ADS1262 e ADS1263 con multiplexer di ingresso analogico a dieci canali. ADS1263 ha un secondo ADC ΔƩ a 24 bit su chip. (Immagine per gentile concessione di Texas Instruments)

Figura 9: Diagramma a blocchi dell'ADC ΔƩ a 32 bit ADS1262 e ADS1263 con multiplexer di ingresso analogico a dieci canali. ADS1263 ha un secondo ADC ΔƩ a 24 bit su chip. (Immagine per gentile concessione di Texas Instruments)

Come per ADS1235, il guadagno PGA, la velocità dati, la modalità di filtro digitale e la modalità chopping sono i principali fattori che influenzano le prestazioni di rumore con ADS1262/63. Con una risoluzione a 32 bit, ADS1262/63 mostra veramente la capacità di profondità a basso rumore.

In primo luogo, un modulatore stabile di quarto ordine e i filtri da sinc1 a sinc4 producono una risoluzione efficace di 32 bit, così come una risoluzione senza rumore di 24 bit. Configurando una bassa frequenza, una velocità dati di 2,5 sps e un guadagno PGA di 1 V/V (bypassato), il rumore del convertitore dell'uscita digitale sinc3 in un sistema a 5 V è di 0,08 mVRMS (0,307 mVPP). Questo dispositivo supera la risoluzione efficace con 26,9 bit, così come una risoluzione senza rumore di 25 bit. Per questo sistema a 32 bit l'SNR teorico è di 387 dB, con SNR efficace pari a 164 dB.

Le differenze tra il rumore dei convertitori a 24 bit e a 32 bit sono evidenti, dove la capacità a 32 bit dell'ADC ΔƩ a basso rumore supera quella dell'ADC ΔƩ a 24 bit (Tabella 2).

*Nota: SNR = 6,02 N + 1,76, dove N è il numero di bit

|

Tabella 2: Confronto tra rumore rms, rumore picco-picco e SNR dell'ADC con tensione di ingresso a fondo scala di 5 V. (Dati per gentile concessione di DigiKey)

Conclusione

L'ADC ΔƩ continua a spingere i limiti del basso rumore con capacità sempre nuove. Questo articolo mostra come questo ADC a basso rumore quasi digitale si presti perfettamente per applicazioni di temperatura, pressione e celle di carico. Una discussione approfondita di un ADC ΔƩ a 24 bit di precisione e di un ADC ΔƩ a 32 bit che delinea il percorso per concretizzare le loro caratteristiche di ultraprecisione.

Esonero della responsabilità: le opinioni, le convinzioni e i punti di vista espressi dai vari autori e/o dai partecipanti al forum su questo sito Web non riflettono necessariamente le opinioni, le convinzioni e i punti di vista di DigiKey o le sue politiche.