Accelerare la progettazione di sistemi di riconoscimento visivo con le MPU serie RZ/V2 di Renesas

Contributo di Editori nordamericani di DigiKey

2022-09-29

Poiché il riconoscimento visivo sull'edge sta diventando sempre più centrale in molti prodotti, l'apprendimento automatico (ML) e l'intelligenza artificiale (IA) si stanno facendo strada in un'ampia gamma di applicazioni. Il problema che gli sviluppatori devono affrontare è che la visione abilitata da ML/IA può richiedere enorme potenza di calcolo per eseguire gli algoritmi di riconoscimento rispetto a quella disponibile nelle applicazioni con vincoli di basso consumo energetico. Inoltre, se sono necessarie costose soluzioni di gestione termica, i costi aumentano.

L'obiettivo di ML/IA sull'edge è trovare l'approccio architettonico ottimale che bilanci prestazioni e potenza, fornendo al contempo un robusto ecosistema software in cui sviluppare l'applicazione.

Tenendo conto di queste condizioni, questo articolo presenta una soluzione sotto forma di unità microprocessore (MPU) serie RZ/V2 di Renesas Electronics con acceleratore hardware IA integrato. L'articolo analizza come una MPU, e non un microcontroller (MCU) o un'unità di elaborazione grafica (GPU) di fascia alta, possa risolvere diversi problemi progettuali. È inclusa una descrizione di come iniziare a progettare sistemi di riconoscimento visivo utilizzando la serie RZ/V2, insieme ad alcuni suggerimenti per facilitare il processo.

Introduzione alle MPU serie RZ/V2

La serie RZ/V2 è una soluzione che propone molte funzionalità agli sviluppatori che utilizzano un microprocessore a tre core. I microprocessori serie RZ/V2L contengono due processori ARM Cortex-A55 a 1,2 GHz e un core di microcontroller in tempo reale (ARM® Cortex®-M33) a 200 MHz. Inoltre, i componenti della serie contengono una GPU basata su un processore multimediale ARM Mali-G31 con istruzioni NEON singole/dati multipli (SIMD). La combinazione di questi tre core di elaborazione e del processore multimediale offre una soluzione completa agli sviluppatori che lavorano sui sistemi di riconoscimento visivo.

Attualmente esistono due classi di MPU nella serie RZ/V2, la serie RZ/V2L e la serie RZ/V2M. RZ/V2L è dotato di un semplice processore di segnali di immagine (ISP), di un motore grafico 3D e di un set di periferiche estremamente versatile. RZ/V2M invece aggiunge un ISP ad alte prestazioni che supporta la risoluzione 4K a 30 fotogrammi al secondo. Questo articolo si concentra sulla famiglia RZ/V2L, composta dai modelli R9A07G054L23GBG e R9A07G054L24GBG. La differenza principale tra i due componenti è che R9A07G054L23GBG è disponibile in un contenitore 456-LFBGA di 15 mm2, mentre R9A07G054L24GBG è disponibile in un contenitore 551-LFBGA di 21 mm2.

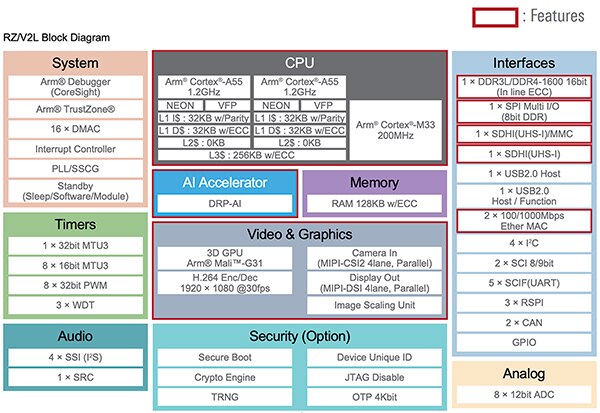

Nella Figura 1 è riportato il diagramma a blocchi della serie RZ/V2L. Oltre ai tre core di elaborazione, le MPU includono interfacce per periferiche standard come memoria DDR3/DDR4, SPI, USB, Ethernet, I²C, CAN, SCI, GPIO e un convertitore analogico/digitale (ADC). Inoltre, i componenti includono funzionalità di sicurezza come l'avvio sicuro, un motore di crittografia e un generatore di numeri casuali reali (TRNG). Ciò che distingue la serie MPU, tuttavia, è l'acceleratore IA DRP (Dynamically Reconfigurable Processor).

Figura 1: La serie di MPU RZ/V2L supporta diverse interfacce periferiche, opzioni di sicurezza e di elaborazione video. La caratteristica fondamentale per le applicazioni di riconoscimento visivo è l'acceleratore DRP-AI. (Immagine per gentile concessione di Renesas Electronics Corporation)

Figura 1: La serie di MPU RZ/V2L supporta diverse interfacce periferiche, opzioni di sicurezza e di elaborazione video. La caratteristica fondamentale per le applicazioni di riconoscimento visivo è l'acceleratore DRP-AI. (Immagine per gentile concessione di Renesas Electronics Corporation)

L'ingrediente segreto dell'acceleratore DRP-AI

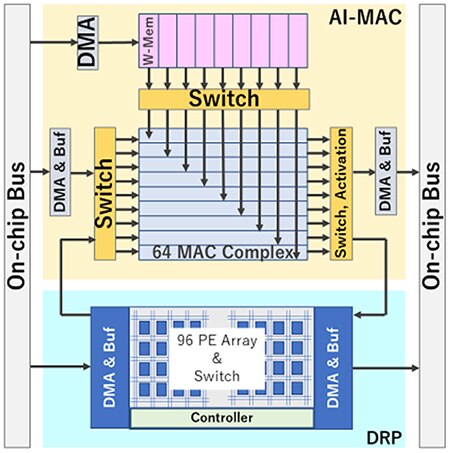

L'acceleratore DRP-AI è l'ingrediente segreto che consente alle MPU serie RZ/V2L di eseguire applicazioni di riconoscimento visivo in modo rapido, con un consumo energetico minore e un profilo termico più basso. DRP-AI comprende due componenti: un DRP e un MAC (IA-moltiplicatore-accumulatore), in grado di elaborare in modo efficiente le operazioni nelle reti convoluzionali e nei livelli combinanti, ottimizzando il flusso di dati con switch interni (Figura 2).

L'hardware DRP-AI è dedicato all'esecuzione dell'inferenza IA. DRP-AI utilizza un'esclusiva tecnologia riconfigurabile dinamica sviluppata da Renesas che garantisce flessibilità, elaborazione ad alta velocità ed efficienza energetica. Inoltre, il traduttore DRP-AI, uno strumento software gratuito, consente agli utenti di implementare modelli di intelligenza artificiale ottimizzati che massimizzano rapidamente le prestazioni. È possibile collocare nella memoria esterna diversi eseguibili prodotti dal traduttore DRP-AI. L'applicazione può quindi passare dinamicamente tra svariati modelli IA durante il runtime.

DRP è in grado di elaborare rapidamente attività complesse come la preelaborazione delle immagini e i livelli di pooling dei modelli di intelligenza artificiale modificando dinamicamente la configurazione hardware.

Figura 2: DRP-AI comprende un DRP e un AI-MAC, che insieme sono in grado di elaborare in modo efficiente le operazioni nelle reti convoluzionali e nei livelli combinanti ottimizzando il flusso di dati con switch interni. (Immagine per gentile concessione di Renesas Electronics Corporation)

Figura 2: DRP-AI comprende un DRP e un AI-MAC, che insieme sono in grado di elaborare in modo efficiente le operazioni nelle reti convoluzionali e nei livelli combinanti ottimizzando il flusso di dati con switch interni. (Immagine per gentile concessione di Renesas Electronics Corporation)

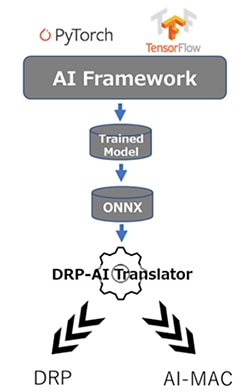

Il traduttore DRP-AI

Il traduttore DRP-AI genera eseguibili ottimizzati DRP-AI da modelli ONNX addestrati, indipendentemente dal framework di IA. Ad esempio, uno sviluppatore può usare PyTorch, TensorFlow o qualsiasi altro framework di modellazione IA se produce un modello ONNX. Una volta addestrato, il modello viene inserito nel traduttore DRP-AI, che genera gli eseguibili DRP e AI-MAC (Figura 3).

Figura 3: I modelli IA vengono addestrati utilizzando un qualsiasi framework compatibile con ONNX. Il modello ONNX viene quindi inserito nel traduttore DRP-AI, che genera gli eseguibili DRP e AI-MAC. (Immagine per gentile concessione di Renesas Electronics Corporation)

Figura 3: I modelli IA vengono addestrati utilizzando un qualsiasi framework compatibile con ONNX. Il modello ONNX viene quindi inserito nel traduttore DRP-AI, che genera gli eseguibili DRP e AI-MAC. (Immagine per gentile concessione di Renesas Electronics Corporation)

Il traduttore DRP-AI ha tre scopi principali:

- Pianificazione di ogni operazione di elaborazione del modello IA.

- Nascondere il sovraccarico, come il tempo di accesso alla memoria che si verifica durante la transizione di ogni operazione, nella pianificazione.

- Ottimizzazione della struttura del grafo di rete.

Il traduttore assegna automaticamente ogni processo del modello IA all'AI-MAC e al DRP, consentendo all'utente di utilizzare facilmente DRP-AI senza bisogno di essere esperti di hardware. Lo sviluppatore può invece effettuare chiamate attraverso il driver fornito per eseguire il modello IA ad alte prestazioni. Inoltre, il traduttore DRP-AI può essere continuamente aggiornato per supportare i nuovi modelli IA sviluppati senza modifiche hardware.

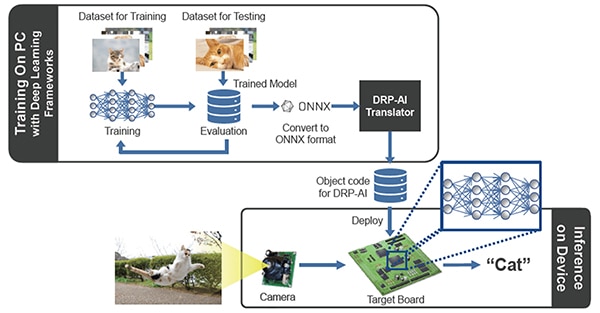

Casi d'uso e processi del sistema

Il flusso di processo generale per l'utilizzo delle MPU RZ/V2L per l'addestramento e l'implementazione di applicazioni di riconoscimento visivo è mostrato nella Figura 4. Come al solito, gli ingegneri possono acquisire il loro set di dati e utilizzarlo per addestrare un particolare modello di riconoscimento della visione. Sia che stiano cercando di identificare gatti, un prodotto in un carrello della spesa o componenti guasti in una catena di montaggio, il processo di addestramento avverrà utilizzando framework di IA già noti. Una volta addestrato, il modello viene convertito in formato ONNX e inserito nel traduttore DRP-AI, che a sua volta produce codice oggetto che può essere eseguito sull'hardware DRP-AI. I dati provenienti da telecamere, accelerometri o altri sensori vengono quindi campionati e inseriti negli eseguibili, fornendo il risultato dell'esecuzione dell'inferenza.

Figura 4: Il processo di addestramento e di esecuzione di un algoritmo di riconoscimento visivo sulle MPU RZ/V2L. (Immagine per gentile concessione di Renesas Electronics Corporation)

Figura 4: Il processo di addestramento e di esecuzione di un algoritmo di riconoscimento visivo sulle MPU RZ/V2L. (Immagine per gentile concessione di Renesas Electronics Corporation)

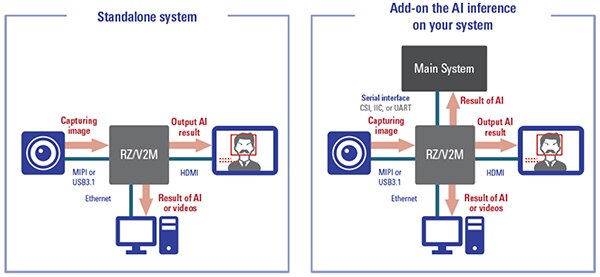

Gli ingegneri possono sfruttare le MPU RZ/V2L in diversi modi nei loro progetti (Figura 5). In primo luogo, la MPU RZ/V2L può essere utilizzata in progetti standalone in cui RZ/V2L è l'unico processore del sistema. Con i suoi tre core e l'hardware di accelerazione IA, la potenza di calcolo aggiuntiva potrebbe non essere necessaria.

Il secondo caso d'uso è quello che vede RZ/V2L utilizzato come processore IA in un sistema più esteso. In questo caso d'uso, RZ/V2L esegue le inferenze dell'intelligenza artificiale e restituisce un risultato a un altro processore o sistema che agisce di conseguenza a tale risultato. Il caso d'uso selezionato dipenderà da vari fattori, quali il costo, l'architettura complessiva del sistema, le prestazioni e i requisiti di risposta in tempo reale.

Figura 5: I due casi d'uso delle MPU RZ/V2L sono l'utilizzo autonomo in un'applicazione o come processore IA in un sistema più esteso. (Immagine per gentile concessione di Renesas Electronics Corporation)

Figura 5: I due casi d'uso delle MPU RZ/V2L sono l'utilizzo autonomo in un'applicazione o come processore IA in un sistema più esteso. (Immagine per gentile concessione di Renesas Electronics Corporation)

Esempio di applicazione reale

Sono molti i casi d'uso in cui può essere impiegata la tecnologia di riconoscimento visivo. Un esempio interessante è quello del supermercato. Oggi, quando si fanno acquisti in un negozio di alimentari, un cassiere di solito scansiona ogni articolo nel carrello. Un caso d'uso interessante potrebbe essere quello di rilevare i prodotti che attraversano il nastro trasportatore grazie al riconoscimento visivo e addebitarli automaticamente.

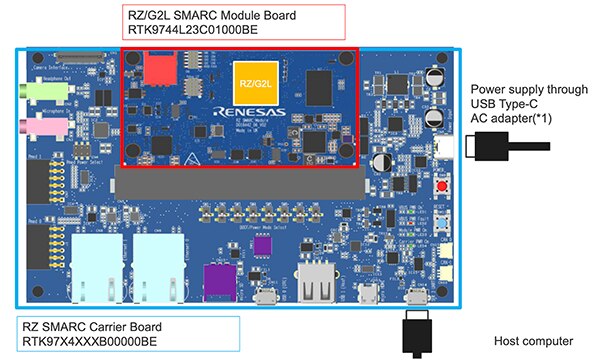

È possibile realizzare un prototipo utilizzando una semplice telecamera CMOS e la scheda di valutazione RTK9754L23S01000BE di Renesas (Figura 6). La scheda di sviluppo embedded RZ/V2L è dotata di un System-on-Module (SoM) e di una scheda portante che consente agli sviluppatori di diventare subito operativi. Inoltre, la scheda di sviluppo supporta Linux e vari strumenti come il traduttore DRP-AI.

Figura 6: La scheda di sviluppo embedded RZ/V2L è dotata di un SoM e di una scheda portante che consentono agli sviluppatori di diventare subito operativi. (Immagine per gentile concessione di Renesas Electronics Corporation)

Figura 6: La scheda di sviluppo embedded RZ/V2L è dotata di un SoM e di una scheda portante che consentono agli sviluppatori di diventare subito operativi. (Immagine per gentile concessione di Renesas Electronics Corporation)

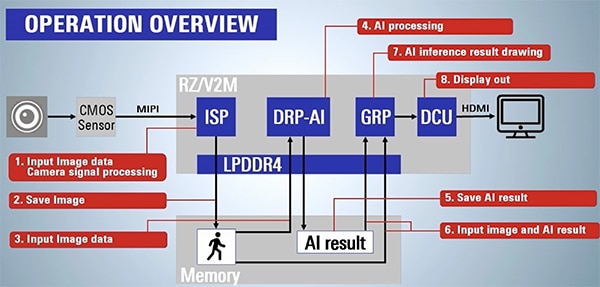

La Figura 7 mostra una panoramica operativa di ciò che è necessario per acquisire i dati delle immagini e produrre un risultato di IA. In questo esempio di applicazione, le immagini del nastro trasportatore vengono riprese con un sensore CMOS attraverso l'ISP su scheda. Successivamente, l'immagine viene salvata in memoria e inserita nel motore DRP-AI. Infine, il motore DRP-AI esegue l'inferenza e fornisce un risultato IA. Ad esempio, il risultato potrebbe essere una banana, una mela o un altro frutto.

Il risultato è spesso accompagnato da un livello di confidenza compreso tra 0 e 1. Ad esempio, 0,90 di confidenza significa che l'intelligenza artificiale è sicura di aver individuato una mela. Per contro, un livello di confidenza di 0,52 potrebbe significare che l'intelligenza artificiale pensa che si tratti di una mela, ma non è sicura. Non è raro che si prenda il risultato IA e si faccia una media tra più campioni per migliorare le probabilità di ottenere risultati corretti.

Figura 7: La scheda di sviluppo embedded RZ/V2L viene utilizzata per eseguire un'inferenza IA che riconosce vari frutti su un nastro trasportatore. La figura mostra i passaggi necessari per acquisire un'immagine e produrre un risultato IA. (Immagine per gentile concessione di Renesas Electronics Corporation)

Figura 7: La scheda di sviluppo embedded RZ/V2L viene utilizzata per eseguire un'inferenza IA che riconosce vari frutti su un nastro trasportatore. La figura mostra i passaggi necessari per acquisire un'immagine e produrre un risultato IA. (Immagine per gentile concessione di Renesas Electronics Corporation)

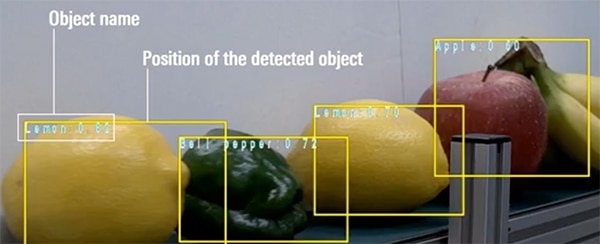

Infine, in questo esempio, viene disegnato un riquadro attorno all'oggetto rilevato e viene visualizzato il nome dell'oggetto riconosciuto insieme al livello di confidenza (Figura 8).

Figura 8: Esempio di risultato prodotto da RZ/V2L in un'applicazione che rileva frutta e verdura su un nastro trasportatore. (Immagine per gentile concessione di Renesas Electronics Corporation)

Figura 8: Esempio di risultato prodotto da RZ/V2L in un'applicazione che rileva frutta e verdura su un nastro trasportatore. (Immagine per gentile concessione di Renesas Electronics Corporation)

Suggerimenti per iniziare a lavorare con RZ/V2L

Gli sviluppatori che desiderano iniziare a lavorare con l'apprendimento automatico sulle MPU RZ/V2L di Renesas scopriranno di avere a disposizione molte risorse da sfruttare da subito. Di seguito sono forniti diversi "suggerimenti" da tenere a mente che possono semplificare e accelerare lo sviluppo, ad esempio:

- Iniziare con una scheda di sviluppo e con gli esempi esistenti, per avere un'idea della distribuzione e dell'esecuzione di un'applicazione.

- Se è necessario eseguire più inferenze, salvare i modelli eseguibili nella memoria esterna e utilizzare le funzionalità di DRP-AI per passare rapidamente da un modello all'altro.

- Studiare la documentazione e guardare i video disponibili sul sito delle MPU IA embedded RZ/V di Renesas.

- Scaricare il traduttore DRP-AI.

- Scaricare il pacchetto di supporto RZ/V2L DRP-AI.

Seguendo questi consigli, gli sviluppatori risparmieranno parecchio tempo nel processo di sviluppo.

Conclusione

L'apprendimento automatico e l'intelligenza artificiale si stanno facendo strada in molte applicazioni sull'edge. La capacità di riconoscere gli oggetti in tempo reale diventa sempre più importante. Per i progettisti, la difficoltà consiste nel trovare l'architettura giusta con cui eseguire l'IA/ML sull'edge. Le GPU tendono ad essere energivore, mentre le MCU potrebbero non avere una potenza di calcolo sufficiente.

Come dimostrato, la serie di MPU RZ/V con DRP-AI di Renesas offre diversi vantaggi, come IA accelerata dall'hardware, oltre a un'ampia gamma di strumenti e al supporto per la prototipazione.

Esonero della responsabilità: le opinioni, le convinzioni e i punti di vista espressi dai vari autori e/o dai partecipanti al forum su questo sito Web non riflettono necessariamente le opinioni, le convinzioni e i punti di vista di DigiKey o le sue politiche.