Verwendung eines einzelnen, extrem energieeffizienten HMP-Prozessors für Echtzeit- und Anwendungsverarbeitung

Zur Verfügung gestellt von Nordamerikanische Fachredakteure von DigiKey

2019-08-06

Die Verbraucher wünschen sich Unterhaltungselektronik und andere Mobilgeräte, die sowohl schneller reagieren als auch mehr Funktionen bieten – und das alles bei einer längeren Batterielebensdauer. Um den Anforderungen nach Echtzeit-Reaktionen und hoher Leistung jedoch gerecht werden zu können, sahen sich die Entwickler dazu gezwungen, separate Prozessoren zu verwenden. Nur so konnten sie diesen widersprüchlichen Anforderungen entsprechen. Dadurch erhöhten sich jedoch die Kosten, der Stromverbrauch und der Platzbedarf und das Hardwarelayout und die Software wurden komplexer.

Ein besserer Ansatz wäre, die erforderliche Hardware in einen einzelnen Chip zu integrieren. Und genau hier kommen HMP-Komponenten mit heterogener Multicore-Verarbeitung ins Spiel. Mit mehreren unterschiedlichen Kernen bieten diese Prozessoren Vorteile wie Leistungsoptimierung, reduzierte Leistungsaufnahme und verbesserte Systemsicherheit und -zuverlässigkeit.

Dieser Artikel beschreibt, wie Entwickler den heterogenen Multicore-Prozessor von NXP Semiconductors verwenden können, um den Anforderungen dieser gemischten Aufgaben gerecht zu werden, ohne Kompromisse hinsichtlich Energieeffizienz und Designkomplexität eingehen zu müssen.

Anforderungen im Wandel

Fortschritte bei Sensortechnologie und Datenverarbeitungsalgorithmen geben Entwicklern völlig neue Möglichkeiten an die Hand, um die widersprüchlichen Anforderungen der Echtzeit-Datenerfassung und der rechenintensiven Ausführung von Algorithmen in den Griff zu bekommen. Früher haben die Entwickler diese Aufgaben üblicherweise auf separate Systeme aufgeteilt.

Auf der untersten Ebene der Netzwerkhierarchie solcher Systeme werden von eingebetteten Prozessoren, die beispielsweise auf dem Arm®-Cortex®-M4-Kern basieren, Daten erfasst, indem optimierter Code auf einem Echtzeitbetriebssystem (Real-Time Operating System, RTOS) oder einem Bare-Metal-System ausgeführt wird. Auf einer höheren Ebene der Hierarchie hingegen führen leistungsstarke Anwendungsprozessoren, die etwa auf dem Arm-Cortex-A7-Kern basieren können, Algorithmen zur Datenanalyse aus, wobei der Anwendungscode auf bekannten Betriebssystemen wie Linux oder Android ausgeführt wird.

Durch den Aufstieg des Edge Computing wurde die Ausführung von Anwendungscode näher an die Datenquelle verlagert. In der Tat wurden die Anforderungen an die Anwendungsverarbeitung – dadurch, dass komplexere Analysealgorithmen schnellere Reaktionen erfordern – nunmehr direkt in die Endgeräte selbst verschoben. Verbraucher erwarten in zunehmendem Maße, dass ausgeklügelte Analysefunktionen inklusive Methoden der künstlichen Intelligenz in Geräte wie IoT-Sensoren, Wearables und andere energieeffiziente Produkte integriert sind.

Die Rolle der heterogenen Multicore-Verarbeitung

Durch das Aufkommen von HMP-Komponenten, die eingebettete Prozessoren und Anwendungsprozessoren in sich vereinen, können Entwickler die gemischten Aufgaben in vielen Anwendungen effizienter bewältigen. HMP-Prozessoren integrieren verschiedene Kerne, von denen jeder für verschiedene Anforderungen im Zusammenhang mit der Aufgabenlast des Zielprodukts optimiert ist. Mit der Prozessorfamilie i.MX 7ULP (Ultra-Low-Power) von NXP können Entwickler die Leistungsfähigkeit einer HMP-Architektur nutzen, um der kompromisslosen Forderung der Kunden nach hoher Leistung und langer Batterielebensdauer in ULP-Produkten der nächsten Generation nachzukommen.

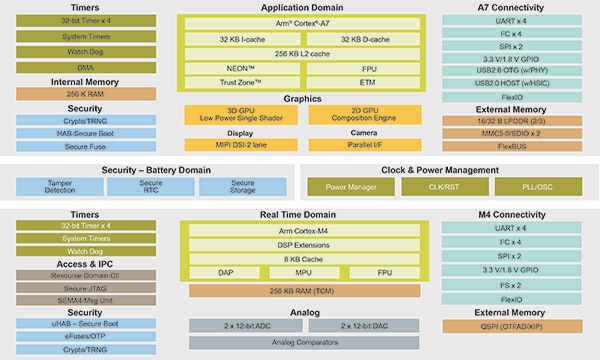

Die sowohl in Verbraucher- (MCIMX7U5DVP07SC) als auch in Industrieversionen (MCIMX7U5CVP06SC) erhältlichen i.MX-7ULP-Prozessoren integrieren ihre heterogenen Kerne mit Grafikprozessoren (GPUs), Sicherheitsbeschleunigern, Speichercontrollern und umfangreichen Peripherieschnittstellen (Abbildung 1).

Abbildung 1: Neben einer großen Auswahl an Modulen und Peripheriebausteinen kombinieren die Anwendungsprozessoren der i.MX-7ULP-Familie von NXP einen Arm-Cortex-M4-Kern zur Echtzeitverarbeitung mit einem Arm-Cortex-A7-Kern zur Anwendungsverarbeitung. Sie verwenden separate Leistungsbereiche zur Optimierung von Stromverbrauch und Leistung. (Bildquelle: NXP)

Abbildung 1: Neben einer großen Auswahl an Modulen und Peripheriebausteinen kombinieren die Anwendungsprozessoren der i.MX-7ULP-Familie von NXP einen Arm-Cortex-M4-Kern zur Echtzeitverarbeitung mit einem Arm-Cortex-A7-Kern zur Anwendungsverarbeitung. Sie verwenden separate Leistungsbereiche zur Optimierung von Stromverbrauch und Leistung. (Bildquelle: NXP)

Die speziell für portable Designs mit Beschränkungen hinsichtlich des Stromverbrauchs konzipierte Familie i.MX 7ULP von NXP nimmt sich neuer Anforderungen an, indem sie einen Arm-Cortex-A7-Kern und einen Cortex-M4-Kern kombiniert, von denen jeder über eine separate Leistungsdomäne verfügt. Zusätzlich ermöglichen verschiedene Stromversorgungsinseln das selektive Abschalten unterschiedlicher Module, wenn diese nicht benötigt werden. Wie nachfolgend beschrieben, ermöglichen die ausgeklügelten Energieverwaltungsfunktionen, die in i.MX-7ULP-Komponenten integriert sind, Entwicklern die Verwendung dieser Leistungsdomänen und Stromversorgungsinseln, um Leistung und Stromverbrauch an ihre Anwendungen anzupassen.

Leistungsoptimierung

Beim Design der i.MX-7ULP-Familie hat NXP Funktionen zur Optimierung von Stromverbrauch und Leistung in die Komponenten integriert, sowohl auf Chip-Ebene als auch in der gesamten Architektur.

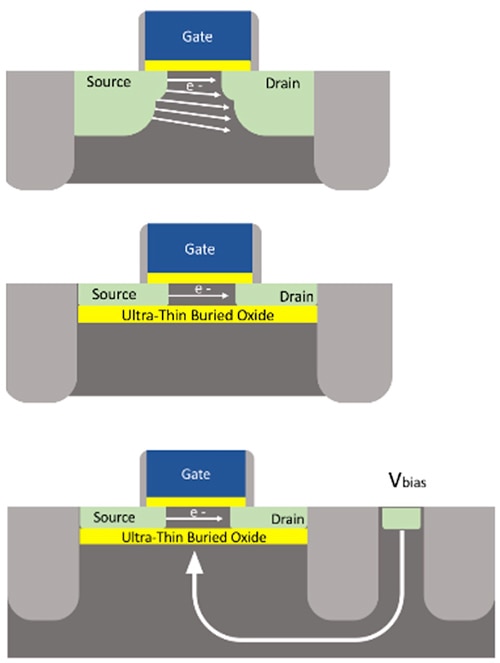

Auf der grundlegendsten Ebene kombiniert die i.MX-7ULP-Familie Fertigungsverfahren zur Senkung des Leckstroms mit Transistorgeometrien, die parasitäre Effekte verringern, wodurch der dynamische Stromverbrauch gesenkt wird. Im Gegensatz zu herkömmlichen Transistorstrukturen (Abbildung 2, oben) werden i.MX-7ULP-Komponenten mit einer hauchdünnen vergrabenen Oxidschicht (Abbildung 2, mittig) gefertigt, die den Elektronenfluss von der Quelle zur Senke und somit den Leckstrom verringert. Eine weitere Verbesserung gestattet den Entwicklern die Integration von Forward Body Biasing (FBB) oder Reverse Body Biasing (RBB) (Abbildung 2, unten).

Abbildung 2: Bei einem herkömmlichen Transistor können beträchtliche Leckströme auftreten, wenn Elektronen von der Quelle zur Senke fließen (oben). Die i.MX-7ULP-Familie von NXP jedoch wird mit einer hauchdünnen vergrabenen Oxidschicht gefertigt, die den Elektronenfluss behindert (mittig), und verfügt außerdem über eine Struktur, die den Elektronenfluss durch Forward Body Biasing (FBB) oder Reverse Body Biasing (RBB) weiter beschleunigt oder verlangsamt (unten). (Bildquelle: NXP)

Abbildung 2: Bei einem herkömmlichen Transistor können beträchtliche Leckströme auftreten, wenn Elektronen von der Quelle zur Senke fließen (oben). Die i.MX-7ULP-Familie von NXP jedoch wird mit einer hauchdünnen vergrabenen Oxidschicht gefertigt, die den Elektronenfluss behindert (mittig), und verfügt außerdem über eine Struktur, die den Elektronenfluss durch Forward Body Biasing (FBB) oder Reverse Body Biasing (RBB) weiter beschleunigt oder verlangsamt (unten). (Bildquelle: NXP)

Wenn es vor allem auf Energieeffizienz ankommt, können die Entwickler mithilfe von RBB den Elektronenfluss verringern und dadurch den Leckstrom sowie den insgesamten Stromverbrauch der Komponente weiter senken, was jedoch zu Lasten der Leistung geht. Umgekehrt können sie den Elektronenfluss mithilfe von FBB erhöhen, um die Leistung zu steigern. Dies hat aufgrund des höheren Leckstroms jedoch einen höheren Stromverbrauch zur Folge.

Auf der Chip-Ebene bietet die i.MX-7ULP-Familie verschiedene Verfahren wie dynamische Frequenzskalierung (DFS) und dynamische Spannungsskalierung (DVS), softwarebasiertes Clock-Gating und softwarebasiertes Power-Gating. Außer zur Senkung des Stromverbrauchs verschiedener Peripheriebausteine können die Entwickler diese Funktionen verwenden, um interne Speicherblöcke selektiv abzuschalten oder den Speicher in diverse Stromsparmodi zu versetzen.

Auf Architekturebene stehen durch die Verwendung mehrerer Leistungsdomänen – inklusive der bereits erwähnten separaten Leistungsdomänen für die Cortex-A7- und Cortex-M4-Subsysteme – weitere Möglichkeiten zur Optimierung von Stromverbrauch und Leistung zur Verfügung.

Jede der Leistungsdomänen der Prozessorkerne umfasst FBB- und RBB-Treiber, LDO-Regler (Low-Dropout) sowie High-Level- (HVDs) und Low-Level-Detektoren (LVDs), die anzeigen, wenn die Versorgungsspannung festgelegte Schwellenwerte über- oder unterschreitet. Ein separater Power-on-Reset (PoR) verfolgt den Spannungspegel in der Always-on-Leistungsdomäne.

Neben den separaten Leistungsdomänen für die Kerne steuern individuelle Leistungsdomänen Systemfunktionen wie die Always-on-Hardware, während eine batteriegestützte Domäne die Stromversorgung kritischer Funktionen verwaltet, z. B. des Echtzeittaktgebers und eines SNVS-Moduls (Secure Non-Volatile Storage). Wie die Leistungsdomänen der Kerne auch, unterstützt jede dieser speziellen Leistungsdomänen einen umfassenden Satz spezieller Stromsparfunktionen (die aufgrund ihrer Vielzahl in nur einem Artikel nicht alle behandelt werden können).

Daher soll hier exemplarisch die Leistungsdomäne für die Always-on-Funktion genannt werden, die ein LLWU-Modul (Low-Leakage Wake-Up Unit) umfasst, mit der die Entwickler mehrere externe Pins oder interne Module als Wake-up-Quelle für spezielle, nachfolgend beschriebene Leistungsmodi bei geringen Leckströmen verwenden können.

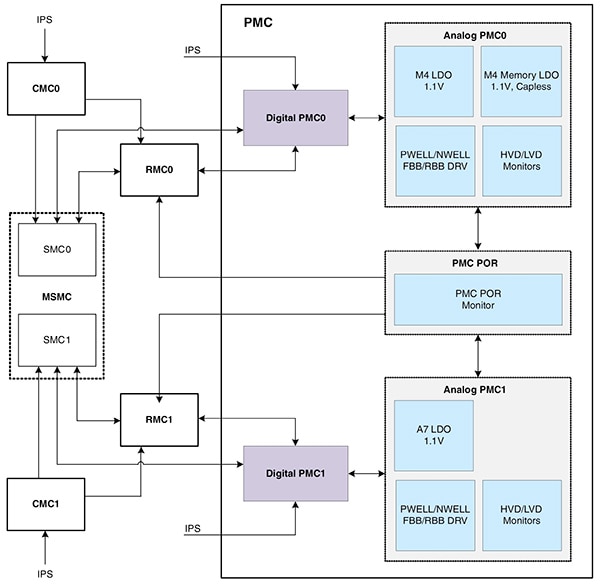

Diese Funktionen auf Architekturebene sind im integrierten Energiemanagement-Controller (PMC, Power Management Controller) gebündelt, der für diese separaten Leistungsdomänen und die Stromversorgungsinseln der Komponente zuständig ist (Abbildung 3).

Abbildung 3: Die i.MX-7ULP-Familie von NXP bietet eine ausgeklügelte Steuermöglichkeit, mit der die Entwickler die Leistungsdomänen und Stromversorgungsinseln programmgesteuert konfigurieren können, um Stromverbrauch und Leistung an die sich ändernden Anforderungen der Anwendung anzupassen. (Bildquelle: NXP)

Abbildung 3: Die i.MX-7ULP-Familie von NXP bietet eine ausgeklügelte Steuermöglichkeit, mit der die Entwickler die Leistungsdomänen und Stromversorgungsinseln programmgesteuert konfigurieren können, um Stromverbrauch und Leistung an die sich ändernden Anforderungen der Anwendung anzupassen. (Bildquelle: NXP)

Bei diesem Ansatz initiieren die Entwickler Übergänge in die Energiesparmodi, indem sie Befehle über den normalen IPS-Bus (Intelligent Peripheral Subsystem) an einen Steuerkomplex senden, der die folgenden drei eng gekoppelten Module umfasst:

- Der Core Mode Controller (CMC) unterstützt mehrere Kernfunktionen.

- Der Multicore System Mode Controller (MSMC), der den System Mode Controller 0 (SMC0) für die Leistungsdomänen des Cortex-M4 und den SMC1 für die Leistungsdomäne des Cortex-A7 umfasst, ist für die Sequenzierung zwischen den verschiedenen Energiesparmodi zuständig, überwacht Ereignisse zur Initiierung von Übergängen zwischen den Energiesparmodi und steuert Stromversorgung, Taktung und Speicherfunktionen im Zusammenhang mit der Leistungsoptimierung.

- Der Reset Mode Controller (RMC) ist für die Reset-Funktionen des Chip zuständig.

Abstimmung von Stromverbrauch und Leistung

Die i.MX-7ULP-Familie bietet den Entwicklern für alle ihre Energiemanagementfunktionen ein vertrautes Programmiermodell. Wie andere moderne Prozessoren auch, bieten i.MX-7ULP-Komponenten verschiedene Betriebsmodi mit geringem Stromverbrauch, indem sie eine Reihe programmierbarer Energiesparmodi verwenden. In der Tat unterstützen die i.MX-7ULP-Prozessorkerne mehrere softwaregesteuerte Energiesparmodi, mit deren Hilfe die Entwickler den Stromverbrauch so weit wie möglich senken können, ohne den erforderlichen Funktionsumfang zu beeinträchtigen.

Mit diesen verschiedenen Energiesparmodi können die Entwickler einen oder beide Kerne sowie ihre Subsysteme in verschiedene Variationen aus einem normalem RUN-Modus, WAIT-Modus und STOP-Modus versetzen.

Der normale RUN-Modus und der HSRUN-Hochgeschwindigkeitsmodus ermöglichen den Hochleistungsbetrieb, um rechenintensive Bereiche einer Anwendung zu unterstützen. Im HSRUN-Modus wird das Subsystem des Kerns mit der maximalen Frequenz betrieben. Ist für die Anwendung auch eine geringere Leistung ausreichend, können die Entwickler den Kern in den VLPR-Modus (Very Low Power Run) für den Betrieb mit einer maximalen Frequenz von 48 Megahertz (MHz) und entsprechend niedrigerem Stromverbrauch versetzen.

Im normalen WAIT-Modus werden die Peripheriebausteine vollständig mit Strom versorgt, wohingegen für den Kern Clock-Gating angewendet wird. Das bedeutet, dass sich der Kern in einem statischen Zustand befindet und darauf wartet, von einem WFI-Signal (Wait-For-Interrupt) aktiviert zu werden. Mit diesem Modus können die Entwickler von autonom betriebenen Peripheriebausteinen Pufferspeicher füllen lassen oder DMA-Transaktionen (Direct Memory Access) durchführen, um den Systemspeicher zu füllen, bevor ein Interrupt gesendet wird, um den Kern aus dem WAIT-Status zu holen. Der VLPW-Modus (Very Low Power Wait) ermöglicht den weiteren Betrieb der Peripheriebausteine mit der verringerten Frequenz, wendet für die Kerntaktung jedoch Clock-Gating an.

In Anwendungen wie Wearables oder tragbaren Geräten kann es vorkommen, dass Systeme über einen längeren Zeitraum inaktiv sind und nur periodisch eine plötzliche Aktivität auftritt. In diesen Fällen ist die Möglichkeit, Strom zu sparen, für die Batterielebensdauer von großer Bedeutung. Wenn für die Anwendung eine längere Aufwachzeit für den Kern möglich ist, stellt die Möglichkeit, die Komponente in noch tiefere Energiesparmodi als den RUN- oder WAIT-Modus zu versetzen, eine besonders effiziente Option dar. Um diesen Ansatz zu unterstützen, können die Entwickler bei der i.MX-7ULP-Familie jedes Subsystem der Kerne in einen tieferen Energiesparmodus mit unterschiedlich langen Aufwachzeiten versetzen:

- Im STOP-Modus können manche Peripheriebausteine asynchron betrieben werden, wohingegen der Kern in einem statischen Zustand mit Aufwachzeiten von 7 Mikrosekunden (μs) für den Cortex-A7 oder 7 μs für den Cortex-M4 verweilt.

- Im VLPS-Modus (Very Low Power Stop) wird der Betrieb der Peripheriebausteine weiter eingeschränkt, wohingegen der Kern in einem statischen Zustand mit Aufwachzeiten von 21,5 μs (Cortex-A7) oder 9 μs (Cortex-M4) verweilt.

Für Anwendungen mit noch strengeren Anforderungen hinsichtlich des Energieverbrauchs können die Entwickler jeden einzelnen Kern in die folgenden speziellen Modi mit geringem Leckstrom versetzen, die weitere Subsysteme der Komponente herunterfahren:

- LLS-Modus (Low Leakage Stop): In diesem Modus wird für Kern, Bus und Peripheriebausteine Clock-Gating angewendet. Der Kern verbleibt dabei in einem WFI-Zustand, wodurch sich eine Aufwachzeit von 40 μs (Cortex-A7) oder 58 μs (Cortex-M4) ergibt.

- VLLS-Modus (Very Low Leakage Stop): In diesem Modus wird für die gesamte Leistungsdomäne des Kerns Clock-Gating angewendet, wodurch sich noch längere Aufwachzeiten ergeben, nämlich 60 μs für den Cortex-A7 oder 375 μs für den Cortex-M4.

Für einen noch geringeren Stromverbrauch können die Entwickler in manchen Energiesparmodi (z. B. VLPS und LLS) RBB verwenden, was jedoch mit einer Leistungsminderung und einem inkrementellen Anstieg der Aufwachzeit von etwa 2 μs bis 4 μs einhergeht.

Umgekehrt können die Entwickler die Kerne in einem speziellen Hochgeschwindigkeitsmodus (HSRUN) ausführen, wenn rechenintensive Aufgaben verarbeitet werden müssen. Im HSRUN-Modus wechselt der Cortex-A7-Kern von seiner normalen Betriebsfrequenz von 500 MHz in einen Overdrive-Modus mit 720 MHz.

Mit dieser Feinabstimmung können die Entwickler den i.MX 7ULP so konfigurieren, dass er selbst extremen Leistungsanforderungen gerecht wird, ohne auf wichtige Funktionen verzichten zu müssen. Beispielsweise kann es vorkommen, dass für eine Anwendung neben einem möglichst geringen Stromverbrauch die Echtzeit-Funktionen des Cortex-M4-Kerns sowie spezielle Peripheriebausteine und der Speicher des Cortex-A7-Subsystems erforderlich sind. In diesem Fall kann der Entwickler das Subsystem des Cortex-A7 in den STOP- oder VLPS-Modus versetzen und vom Cortex-M4 aus auf seinen Speicher oder seine Peripheriebausteine zugreifen, während dieser Kern seine Echtzeit-Abläufe durchführt. Um den Stromverbrauch noch weiter zu senken, können die Entwickler den Taktgeber des Cortex-M4 verwenden, um die Peripheriebausteine des Cortex-A7 anzusteuern.

Einfache Systemimplementierung

Um mit dem i.MX 7ULP ein Low-Power-System zu implementieren, können die Entwickler zwischen verschiedenen per Software programmierbaren Leistungsmodi und Konfigurationen wählen, um den Anforderungen hinsichtlich Stromverbrauch und Leistung zu entsprechen. Hinsichtlich der Hardware ist das Systemdesign sogar noch einfacher.

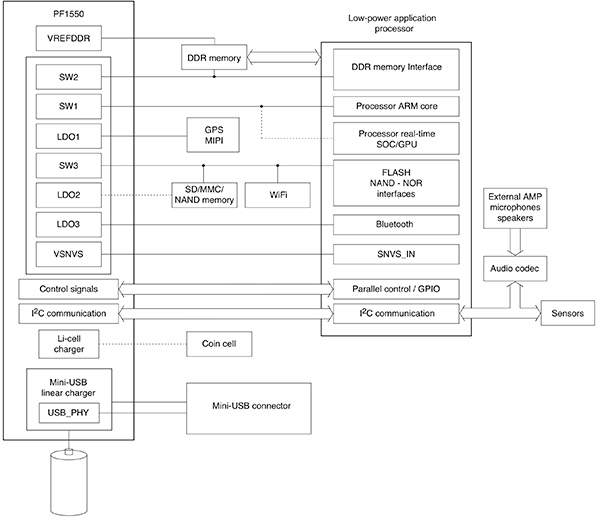

Für typische Anwendungen können die Entwickler einfach einen i.MX-7ULP-Prozessor mit dem zusätzlichen Leistungsmanagement-IC (PMIC) MC32PF1550A3EPR2 von NXP kombinieren, um ein Design zu erhalten, das für gemischte Aufgaben geeignet ist, ohne dabei das begrenzte Strombudget zu beeinträchtigen (Abbildung 4).

Abbildung 4: Der Leistungsmanagement-IC MC32PF1550A3EPR2 von NXP stellt sämtliche Versorgungsquellen zur Verfügung, die vom i.MX-7ULP-Prozessor von NXP benötigt werden. Dadurch reduziert sich das Hardwaredesign auf eine einfache Kombination aus diesen beiden und einigen wenigen passiven Komponenten. (Bildquelle: NXP)

Abbildung 4: Der Leistungsmanagement-IC MC32PF1550A3EPR2 von NXP stellt sämtliche Versorgungsquellen zur Verfügung, die vom i.MX-7ULP-Prozessor von NXP benötigt werden. Dadurch reduziert sich das Hardwaredesign auf eine einfache Kombination aus diesen beiden und einigen wenigen passiven Komponenten. (Bildquelle: NXP)

Der speziell für die Versorgungsanforderungen von NXP-Prozessoren wie die i.MX-7ULP-Familie entwickelte MC32PF1550A3EPR2 integriert drei gesteuerte Abwärtsregler (SW1, SW2 und SW3), drei LDO-Regler (LDO1, LDO2 und LDO3), eine Referenzspannungsquelle für den Speicher, ein Ladegerät für eine Einzelzellen-Lithium-Batterie sowie einen einmal programmierbaren Speicher (OTP, One-Time Programmable) zur Gerätekonfiguration.

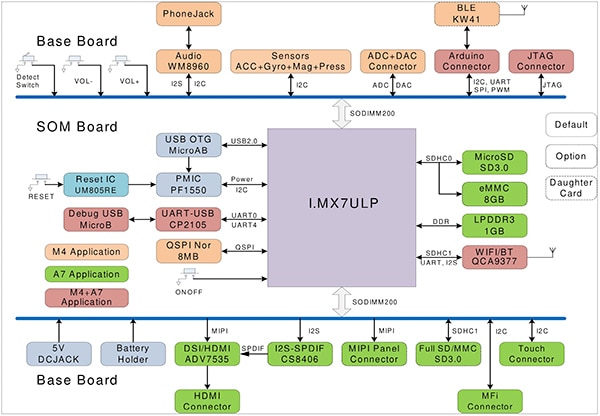

Mit dem Evaluierungskit MCIMX7ULP-EVK stellt NXP eine einfache Hardwareschnittstelle zur Verfügung, mit der der PMIC MC32PF1550A3EPR2 und die i.MX-7ULP-Komponente kombiniert werden können. Neben einem System-on-Module (SOM) mit dem i.MX-7ULP-Prozessor und dem PMIC MC32PF1550A3EPR2 umfasst das Kit eine Grundplatine mit mehreren Sensoren, drahtloser Kommunikation, einem Audio-Codec, einem SD-Steckverbinder sowie verschiedenen anderen Anschlüssen wie JTAG und Arduino (Abbildung 5).

Abbildung 5: Das Evaluierungskit MCIMX7ULP-EVK kombiniert ein System-on-Module mit einem i.MX-7ULP-Prozessor und dem PIMC MC32PF1550A3EPR2 mit einer Grundplatine mit Sensoren, Anschlüssen und weiteren Komponenten, die zur Beschleunigung der Softwareentwicklung mit i.MX 7ULP-Komponenten erforderlich sind. (Bildquelle: NXP)

Abbildung 5: Das Evaluierungskit MCIMX7ULP-EVK kombiniert ein System-on-Module mit einem i.MX-7ULP-Prozessor und dem PIMC MC32PF1550A3EPR2 mit einer Grundplatine mit Sensoren, Anschlüssen und weiteren Komponenten, die zur Beschleunigung der Softwareentwicklung mit i.MX 7ULP-Komponenten erforderlich sind. (Bildquelle: NXP)

Obwohl das Evaluierungskit sofort einsatzbereit ist, stellt NXP den Entwicklern per Download außerdem Designdateien, Tools und Kartenunterstützungspakete für eigene Software zur Verfügung, wobei FreeRTOS für Echtzeitcode und Linux oder Android für Anwendungscode verwendet werden.

Fazit

Um dem Wunsch sowohl nach ausgeklügelteren Funktionen als auch nach längerer Batterielebensdauer in mobilen Produkten entsprechen zu können, mussten die Entwickler üblicherweise gewisse Kompromisse zwischen Stromverbrauch und Leistung eingehen. Weitere Kompromisse zwischen Echtzeitfunktionen und der Leistung auf Anwendungsebene waren erforderlich, weil immer mehr Sensoren in IoT-Geräten, Wearables und sonstigen portablen Produkten immer aktuellere Daten liefern sollten.

Wie man jedoch sehen konnte, können die Entwickler auf HMP-Architekturen wie die in der i.MX-7ULP-Prozessorfamilie von NXP zum Einsatz kommenden zurückgreifen, um den strengen Anforderungen an einen extrem niedrigen Stromverbrauch gerecht zu werden, ohne dabei auf andere Funktionen verzichten zu müssen.

Haftungsausschluss: Die Meinungen, Überzeugungen und Standpunkte der verschiedenen Autoren und/oder Forumsteilnehmer dieser Website spiegeln nicht notwendigerweise die Meinungen, Überzeugungen und Standpunkte der DigiKey oder offiziellen Politik der DigiKey wider.